# THE LAST WORD IN DSP. ZORAN.

Digital Signal Processors Data Book

## **ZORAN**

## PRESIDENT'S MESSAGE

### Dear Customer:

ZORAN Corporation is dedicated to providing system processor solutions for high-performance digital signal processing (DSP) applications. The company designs, manufactures and markets proprietary, monolithic DSP systems processors and associated support tools. By applying its digital signal processing systems and silicon design expertise, ZORAN designs its products top-down with systems requirements foremost in mind. ZORAN's optimized architectures result in powerful, efficient and economical solutions for its customers. A single ZORAN system processor replaces multi-component, board-level products at a fraction of the space, power and cost. ZORAN's highly-integrated, high performance processors result from its distinctive competence in digital signal processing systems, processor architecture, device physics and process technology.

ZORAN's product line consists of two families—Vector Signal Processors (VSP) and Digital Filter Processors (DFP). The VSP family excels at vector operations, including transform computations such as the FFT and the DCT. Theses products are highly integrated, microprocessor-like systems processors, with instruction sets and I/O buses. The DFP Family excels at sums-of-products operations such as Finite Impulse Response (FIR) filters. These products contain multiple arithmetic processors and support sample rates up to 20 MHz.

Support tools for the VSP family include a software simulator and system development environment, a VSP assembler, and two kinds of full-speed VSP hardware development boards. The DFP family support includes a digital filter design software package and a full-speed DFP hardware development board. These constitute complete software and hardware development environments for each product family.

Our worldwide sales, marketing and applications organizations are dedicated to the support of you, the customer. We appreciate your interest and look forward to supplying your present and future requirements.

John a Chiss

## TABLE OF CONTENTS

| 1987 VECTOR SIGNAL PROCESSOR COURSES                           | Absolute Maximum Ratings95                                                  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|

| VECTOR SIGNAL PROCESSORS                                       | Operating Range95                                                           |

| VSP Family Overview                                            | AC Characteristics Over Operating Range95                                   |

| Market Applications                                            | Ordering Information                                                        |

| Functional Applications7                                       | ZR33881 Digital Filter Processor                                            |

| Performance Benchmarks                                         | Distinctive Features99                                                      |

| Description                                                    | Applications99                                                              |

| General Features                                               | Description99                                                               |

| Why the VSP is Unique                                          | Interface Signal Description100                                             |

| Introduction                                                   | Functional Description                                                      |

| Architectural Features8                                        | DFP Filter Cell                                                             |

| Instruction Set Summary                                        | DFP Output Stage                                                            |

| Development Support Tools                                      | DFP Arithmetic                                                              |

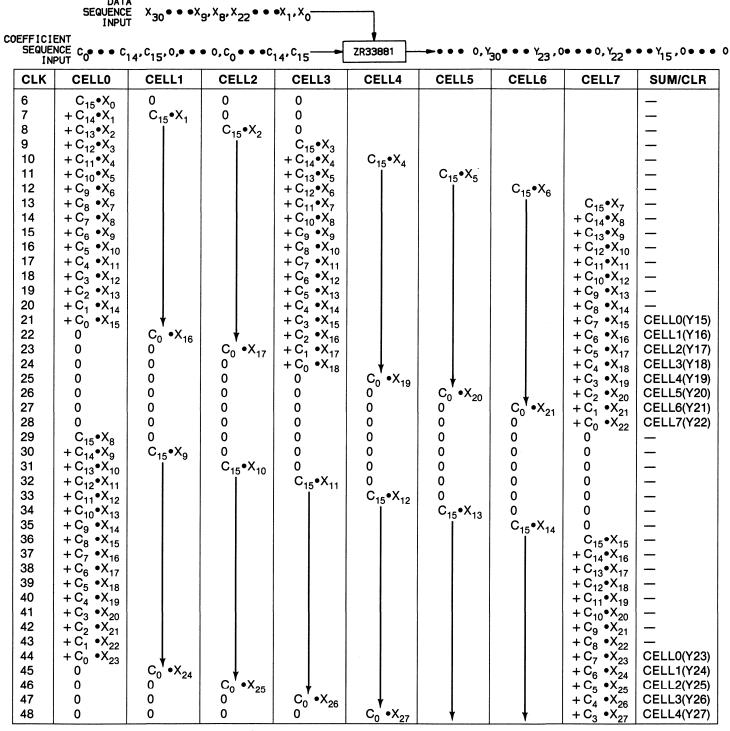

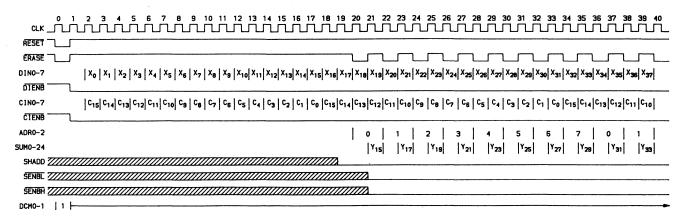

| System Integration                                             | Basic FIR Operation                                                         |

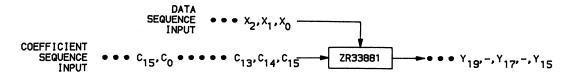

| Multiple-VSP Applications                                      | Extended FIR Filter Length                                                  |

| Programming the VSP                                            | Cascade Configuration                                                       |

| Program Size                                                   | Extended Coefficient and Data Sample Word Size 109                          |

| Block Floating-Point                                           | Decimation/Resampling                                                       |

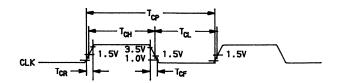

| VSP Application Examples                                       | Other DFP Applications                                                      |

| VSP Simulator                                                  | DFP Timing Parameters                                                       |

| Features                                                       | Absolute Maximum Ratings                                                    |

| Assembler                                                      | Operating Range                                                             |

| VSP Evaluation Package                                         | DC Characteristics Over Operating Range112                                  |

| VSP Development Package                                        | AC Characteristics Over Operating Range113                                  |

| VSP161 Engineering Data Sheet                                  | Ordering Information114                                                     |

| DIGITAL FILTER PROCESSORS                                      | ZR33891 Digital Filter Processor (Preliminary)115                           |

| DFP Family Overview                                            | Distinctive Features115                                                     |

| Preface                                                        | Applications115                                                             |

| Vector Signal Processors (VSP)                                 | Description                                                                 |

| Digital Filter Processors (DFP)                                | Interface Signal Description                                                |

| Market Applications70                                          | Functional Description                                                      |

| Performance Benchmarks                                         | DFP Filter Cell                                                             |

| Functional Applications                                        | The DFP Output Stage                                                        |

| DFP Family Members                                             | Basic FIR Operation                                                         |

| General Features         .70           Description         .71 | Extended FIR Filter Length                                                  |

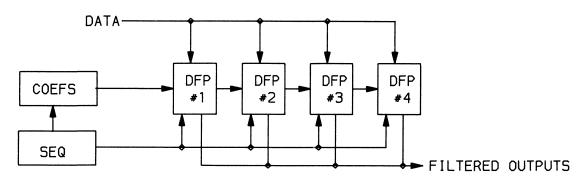

| Why the DFP is Unique71                                        | Cascade Configuration                                                       |

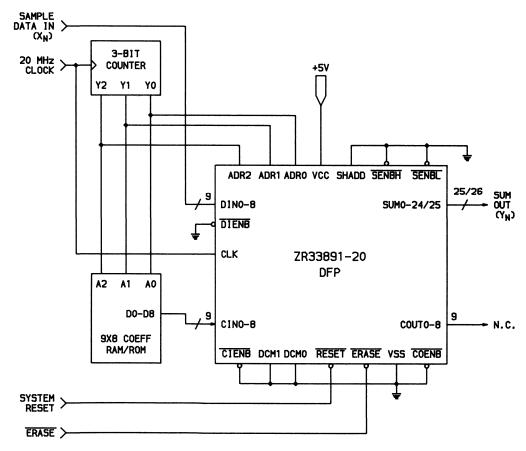

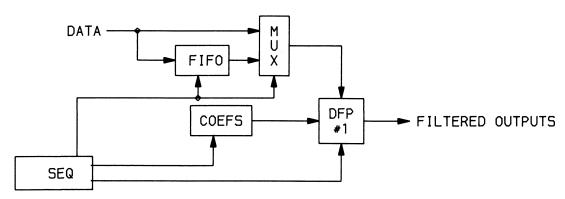

| DFP Configurations                                             | Single DFP Configuration125                                                 |

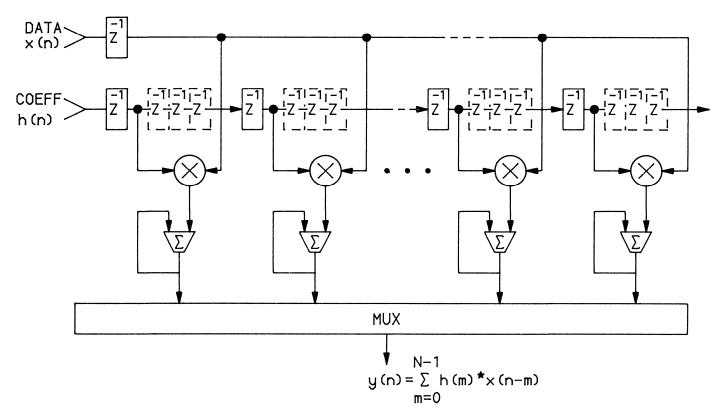

| Basic 1-D Finite Impulse Response (FIR) Filtering              | Extended Coefficient and Data Sample Word Size 126                          |

| Higher Order 1-D Filters                                       | Decimation/Resampling126                                                    |

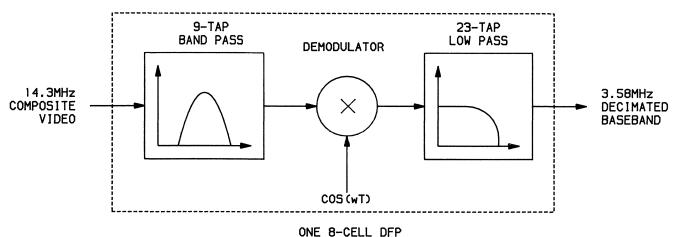

| Decimation74                                                   | Other DFP Applications                                                      |

| Interpolation                                                  | AC Characteristics Over Operating Range129                                  |

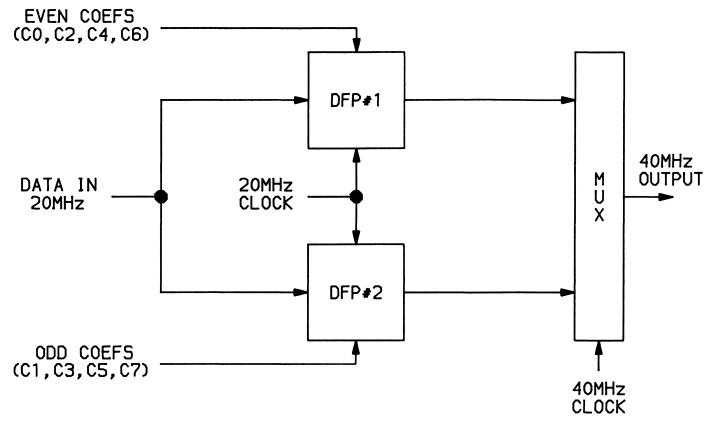

| Higher Sample Rate Filters                                     | Absolute Maximum Ratings130                                                 |

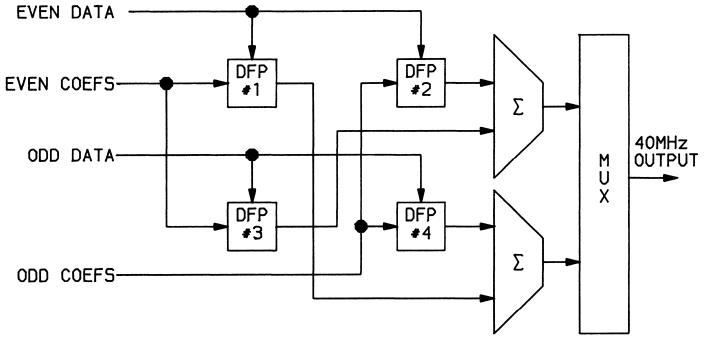

| Higher Precision I-D Filters                                   | Operating Range                                                             |

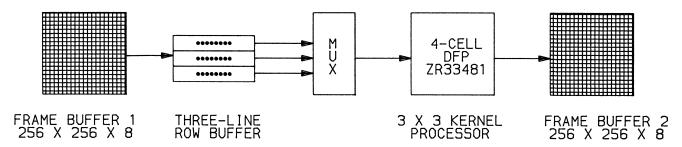

| Two-Dimensional FIR Filters                                    | DC Characteristics Over Operating Range                                     |

| DFP Configuration Selection Guide                              | Ordering Information                                                        |

| DFP Development Tools                                          | ZR33892 Digital Filter Processor                                            |

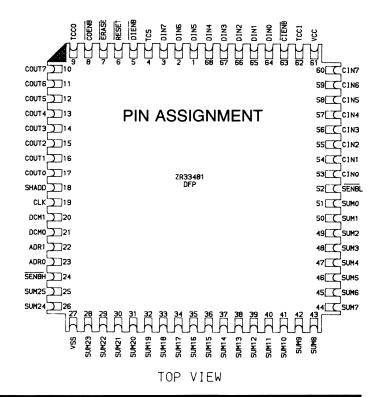

| ZR33481 Digital Filter Processor                               | DEVELOPMENT TOOLS                                                           |

| Distinctive Features                                           | Vector Signal Processor Support Tool Environment137 Development Environment |

| Description                                                    | Development Board Options                                                   |

| Interface Signal Description82                                 | Vector Signal Processor Assembler (VSPA)                                    |

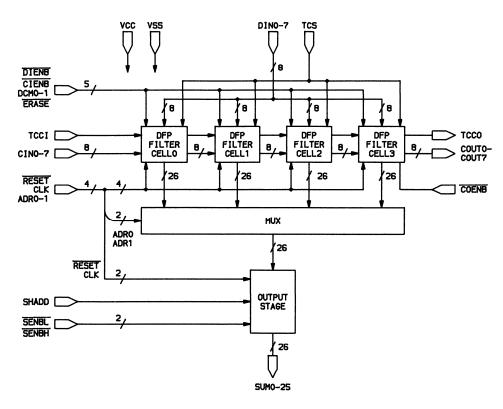

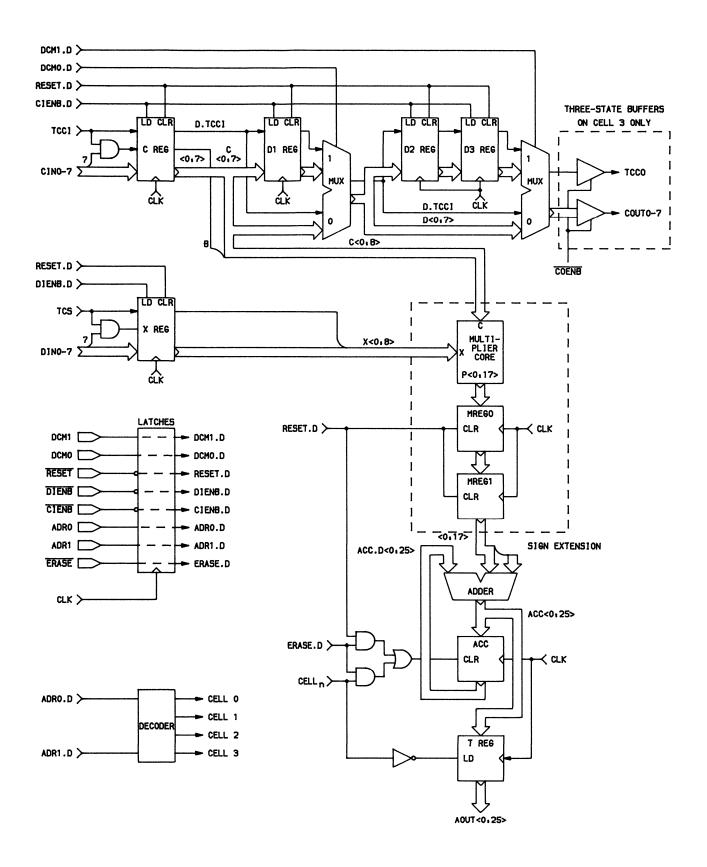

| Functional Description84                                       | Description                                                                 |

| DFP Filter Cell84                                              | Example VSP Program                                                         |

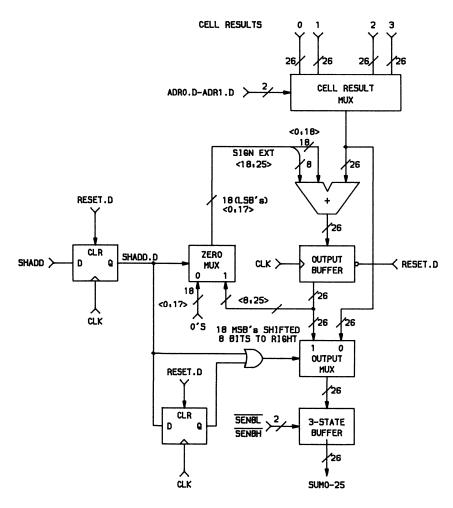

| The DFP Output Stage                                           | Explanation of VSP Program139                                               |

| DFP Arithmetic87                                               | Host Computer Requirements                                                  |

| Basic FIR Operation88                                          | Vector Signal Processor Simulator (VSPS)                                    |

| Extended FIR Filter Length89                                   | Distinctive Features140                                                     |

| Cascade Configuration                                          | Description140                                                              |

| Single DFP Configuration                                       | Simulator Organization                                                      |

| Extended Coefficient and Data Sample Word Size90               | Using the VSP Simulator                                                     |

| Decimation/Resampling                                          | Host Computer Requirements                                                  |

| Other DFP Applications                                         | Feature Variations on Different Computers                                   |

| DFP Timing Parameters94                                        | Ordering Information143                                                     |

|     | VSP Board Support                                                               |      |

|-----|---------------------------------------------------------------------------------|------|

|     | Updates                                                                         | .143 |

| •   | VSP Board Packages                                                              | .144 |

| •   | VSP Board Software                                                              | .144 |

| •   | VSP-161 Programmers Tool Kit                                                    | .144 |

| ,   | VSP Board Applications                                                          | .145 |

|     | VSP Board Hardware                                                              | .145 |

|     | VSPE Hardware                                                                   |      |

|     | VSPX Hardware                                                                   | .147 |

|     | VSPD Hardware                                                                   |      |

|     | Host Computer Requirements                                                      | .150 |

|     | Feature Variations on Different VSP Boards                                      | .150 |

| •   | VSP Logic Analyzer Interface Module                                             | .151 |

|     | Order Information                                                               | .151 |

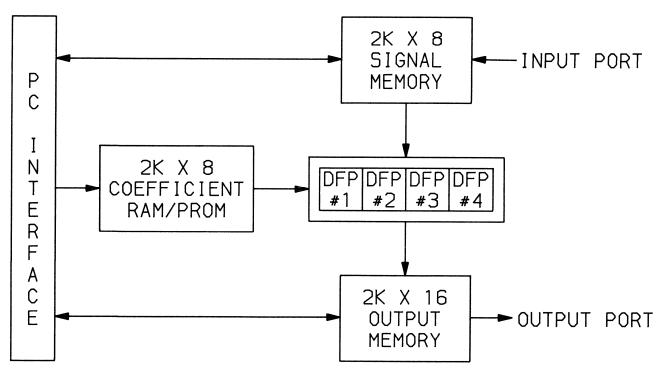

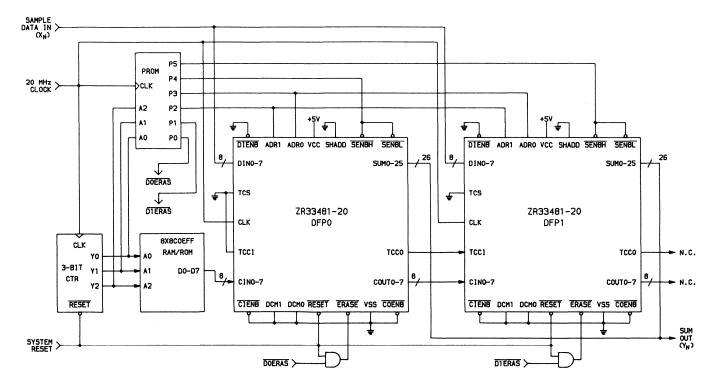

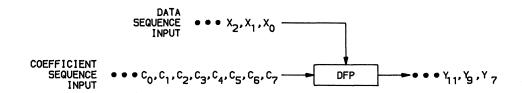

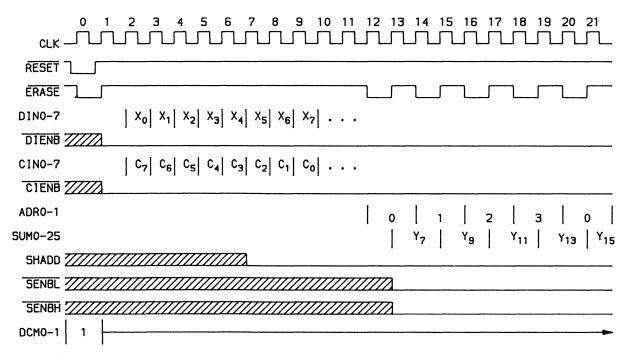

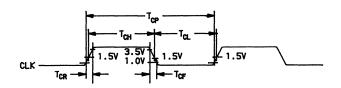

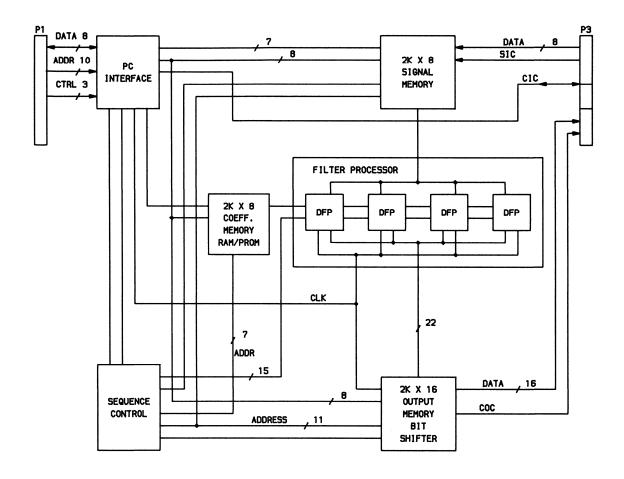

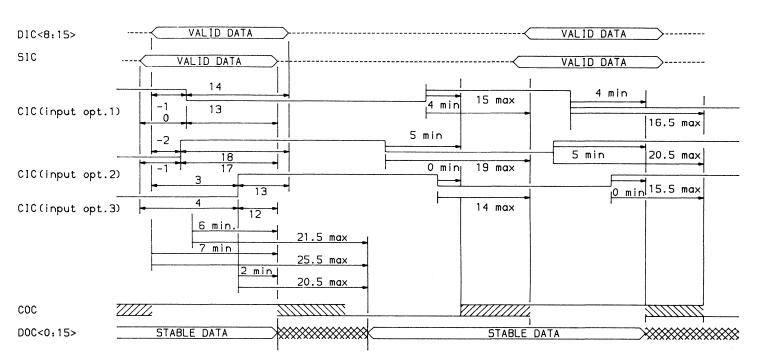

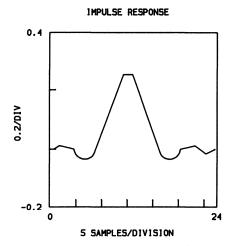

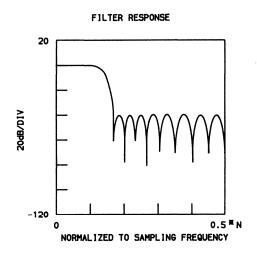

| Dio | ital Filter Processor Board                                                     | 152  |

|     | Distinctive Features                                                            |      |

|     | Description                                                                     |      |

|     | Functional Description                                                          |      |

|     | Board Setup Parameters and Options                                              | 154  |

|     | Sample Rate                                                                     |      |

|     | Precision and Decimation Options                                                | 154  |

|     | Number of Tone                                                                  | .134 |

|     | Number of TapsClock Modes and Synchronizing                                     | .154 |

|     | Operating Environment                                                           | .154 |

|     | Operating Environment                                                           | .155 |

|     | Stand Alone Operation                                                           | .155 |

| ,   | PC/AT or PC/XT with Software Control  PC/AT or PC/XT Operation Without Software | .155 |

|     | Control                                                                         | 155  |

|     | Hardware Interface and Requirements                                             | 155  |

|     |                                                                                 |      |

|     | IBM PC Bus (P1) The DFPB Edge Connector (P3)                                    | .150 |

|     | Board Characteristics                                                           | .150 |

|     | Defenence Decumentation                                                         | .15/ |

|     | Reference Documentation                                                         |      |

|     | Software Requirements                                                           |      |

|     | Product Description/Order Information                                           |      |

|     | gital Filter Software (DFPS)                                                    |      |

|     | Distinctive Features                                                            |      |

|     | Description                                                                     |      |

|     | Filter Design                                                                   | .159 |

|     | Signal Generation                                                               |      |

|     | Signal Filtering                                                                |      |

|     | Transforms                                                                      |      |

|     | Outputs and Displays                                                            |      |

|     | Quantization                                                                    |      |

|     | PROM Programming                                                                |      |

|     | Menu Interface                                                                  |      |

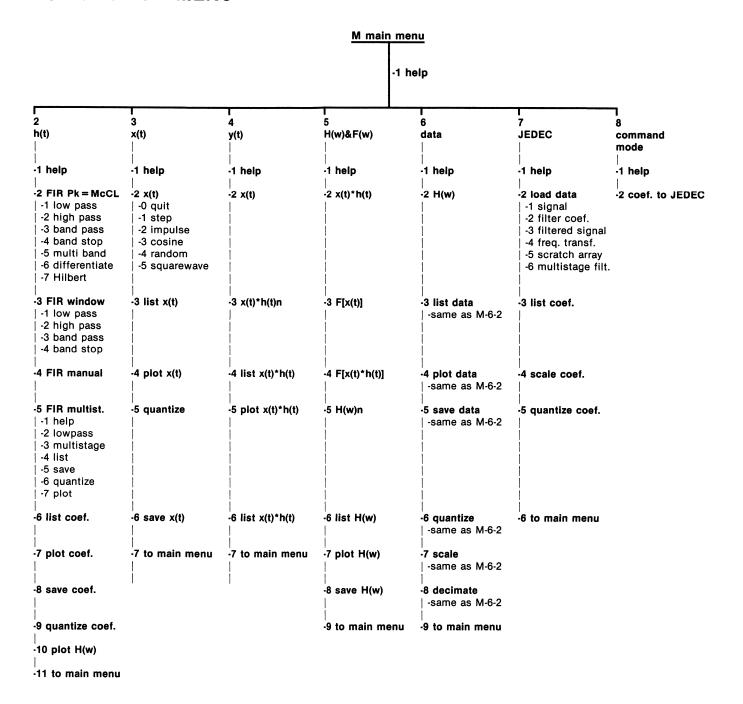

|     | DFPS Function Menu                                                              | .161 |

|     | Command Mode Interface                                                          | .162 |

|     | Hardware Requirements                                                           |      |

|     | Ordering Information                                                            |      |

| Hardware Accessories                                 | 2  |

|------------------------------------------------------|----|

| Operating System Requirements                        | 2  |

| Updates                                              | 2  |

| APPLICATIONS                                         |    |

| <b>VLSI Brochure</b>                                 |    |

| Markets                                              |    |

| Functions                                            | _  |

| Applications                                         |    |

| User Benefits16                                      |    |

| Key Features16                                       |    |

| Introduction                                         |    |

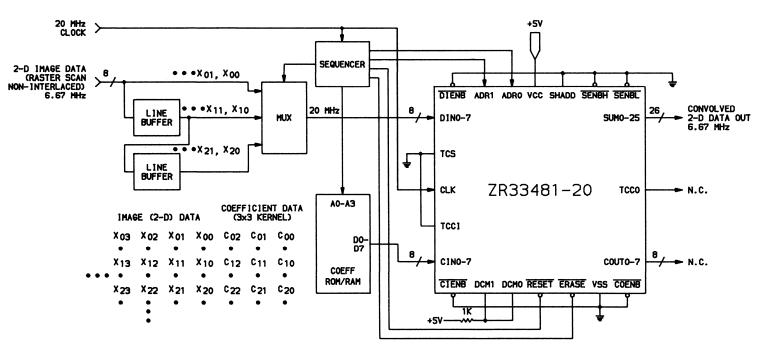

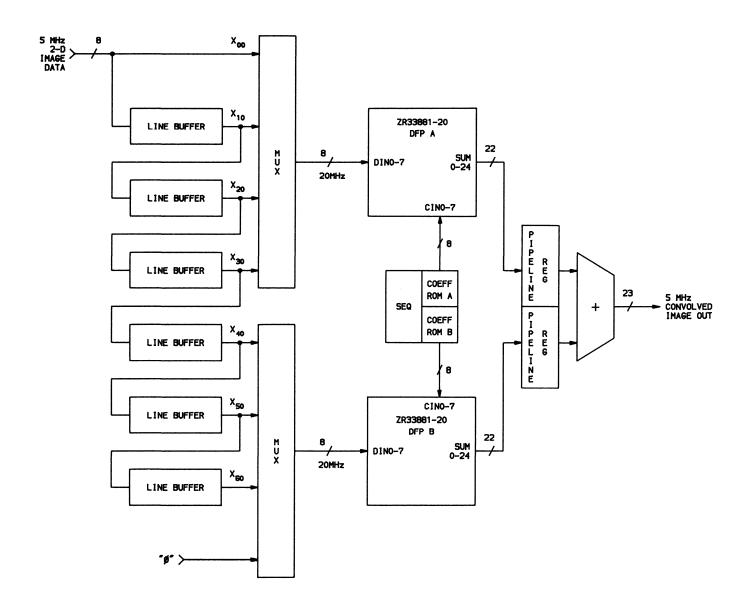

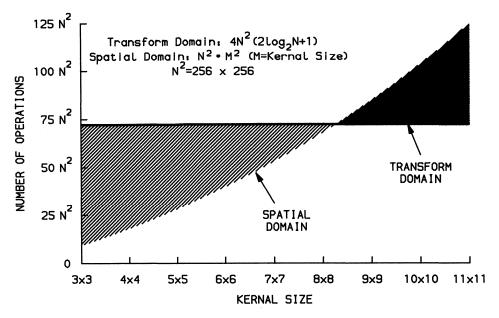

| 2-D Spatial Domain Processing                        | 6  |

| 2-D Spatial Domain Convolution or Correlation 160    |    |

| Edge Detection                                       | 7  |

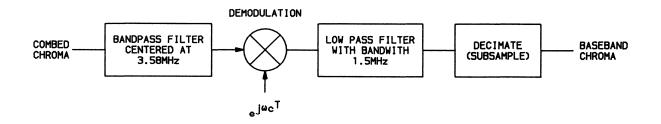

| 1-D Finite Impulse Response (FIR) Filters for        |    |

| Digital Video16                                      | 9  |

| Decimation and Interpolation                         |    |

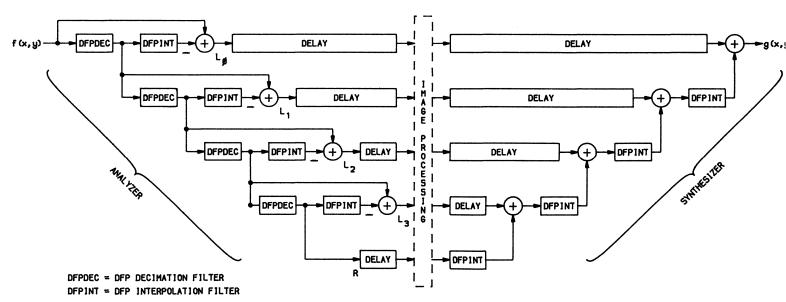

| Pyramid Processing170                                |    |

| Frequency Domain Processing                          |    |

| Processing Unique to the Frequency Domain            | 1  |

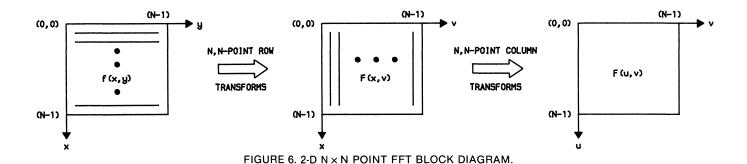

| The Fast Fourier Transform                           | 1  |

| 2-D Fast Convolution or Correlation in the Frequency |    |

| Domain Using the FFT                                 |    |

| Homomorphic or Generalized Linear Filtering174       | 4  |

| Image Compression Using the 2-D Fast Cosine          |    |

| Transform                                            |    |

| Typical Applications                                 |    |

| Machine Vision                                       |    |

| Telecommunications                                   |    |

| Medical Imaging                                      |    |

| Digital Video                                        |    |

| Electronic Cameras                                   |    |

| Military Reconnaissance                              |    |

| Application Listings                                 | 9  |

| Digital VLSI for Broadcast Video                     | 9  |

| VLSI for Industrial Process Monitoring               |    |

| VSP Remote Data Collection and Reduction18           | I  |

| VLSI Digital Signal Processing Solutions for         | _  |

| Medical Equipment                                    | 2  |

| GENERAL INFORMATION                                  | 3  |

| Facilities                                           | _  |

| Reliability and Quality Assurance                    | 0  |

| General                                              |    |

| Quality Planning                                     |    |

|                                                      |    |

| Organization                                         | Ŏ  |

|                                                      | ^  |

| at Zoran                                             |    |

| Lifetest Data at 150°C                               | ノ  |

| Zoran Product Summary Flow                           | プヘ |

| Lotan Froduct Summary Flow                           | U  |

Copyright © 1987 ZORAN Corporation, Santa Clara, California. All rights reserved. Contents of the publication contain proprietary information and may not be reproduced in any form without written permission of ZORAN Corporation.

The material in this manual is for information only. Zoran Corporation assumes no responsibility for errors or omissions and reserves the rights to change, without notice, product specifications, operating characteristics, packaging, etc. Zoran Corporation assumes no liability for damages resulting from the use of information contained in this document.

Vector Signal Processor, VSP, Vector Signal Processor Simulator, and VSPS are trademarks of Zoran Corporation.

DEC, VMS, ULTRIX, and VT100 are trademarks of Digital Equipment Corporation. IBM, PC, PC/XT, and PC/AT are trademarks of International Business Machines. MS-DOS is a trademark of Microsoft Corporation.

## 1987 VECTOR SIGNAL PROCESSOR COURSES

VECTOR SIGNAL PROCESSOR (VSP) AND DEVELOPMENT TOOLS

THREE DAY INTENSIVE LEARNING SESSION\*

OPTIONAL FOURTH DAY FOR APPLICATION ASSISTANCE.

MAY 12-14, 1987 JULY 28-30, 1987 SEPT 29-OCT 1, 1987 DEC 8-10, 1987

## **DESCRIPTION**

ZORAN Corporation is offering its customers a three-day technical training course on the Vector Signal Processor (VSP) and VSP development tools. The course will provide the customer with experience using the VSP Systems Processor, Simulator, and development boards through a series of lectures and hands-on tutorial sessions. After attending the course, participants will be able to apply the VSP to their unique design problems and use the powerful development tools as an aid in the design process.

The primary objectives of this course include: understanding the architecture and operations of the VSP; familiarization with a range of hardware and software interfacing techniques; and providing examples which illustrate how to program the VSP using its high-level instruction set. Sessions on FFT theory and transform domain processing using the VSP are also covered.

In addition, the course offers laboratory sessions on the use of the development tools that will enhance the participants' proficiency in the use of ZORAN's design tools and aids. DSP architecture and systems engineers will also have the opportunity to explore and evaluate new applications using the ZR34161 VSP.

## CONTENTS

**FFT Theory**

## **VSP Hardware**

VSP Memory and Registers VSP Interface Instruction Set Scaling Overlapped Operations System Architecture and Timing VSP Arithmetic

### **VSP Simulator**

VSPS Menus and Signal Generator Lab VSPS Instruction Tutorial Lab Simple VSP Programs and the VSPS High Level Languages VSPS Queueing and Timing

## **VSP Development Boards**

#### VSP Assembler

## VSP/VSPS COURSE OBJECTIVES

- Provide a detailed description of the VSP architecture and thoroughly understand its operation.

- Describe a range of hardware and software interfacing techniques.

- Instruct how to program the VSP using its high level instruction set.

- Demonstrate and understand the use of the VSP Simulator in the designing of VSP-based products.

- Enhance proficiency in the use of ZORAN'S design tools and aids.

- Enable DSP architecture and systems engineers to explore and evaluate new applications for the ZR34161 VSP.

## FEE

\$1,000 per attendee.

## LOCATION

ZORAN Corporation Headquarters 3450 Central Expressway Santa Clara, California 95051

## CONTACT

Course Registrar Tel: (408) 720-0444 ELN: 62942343

## \*PREREQUISITES

Basic DSP experience, prior exposure to FFT techniques and familiarity with contents of VSP engineering data sheets.

# **VECTOR SIGNAL PROCESSORS**

## MARKET APPLICATIONS

- Radar/Sonar

- Image Processing

- **■** Communications

- Image/Data Compression

- Spectral Analysis

- Speech Processing

## **FUNCTIONAL APPLICATIONS**

- 1-D and 2-D FFT

- 1-D and 2-D DCT

- Auto/Cross Correlation

- Convolution/Filtering

- Modulation/Demodulation

- Vector Multiply/Add

| D | E | S | C | R | I | P | T | I | 0 | ١ | Į |

|---|---|---|---|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|---|---|---|---|

The ZR34161 Vector Signal Processor (VSP™) is a member of Zoran's family of high-performance Systems Processors™. The VSP is a 16-bit processor which introduces algorithm-level and vector-oriented instructions to digital signal processing (DSP) system design. It functions as the key element in high-performance DSP applications. In coordination with a host controller, the VSP performs computation-intensive tasks while making minimum demands on host resources and system I/O capacity.

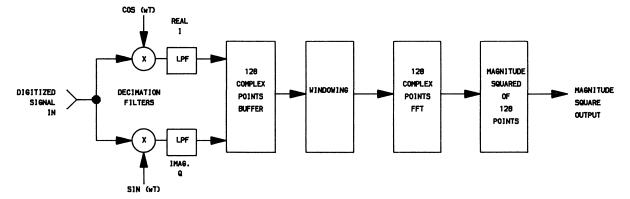

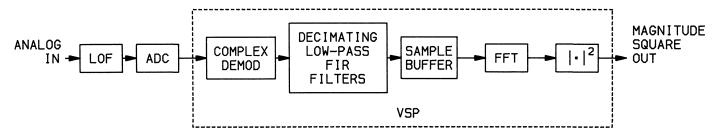

The block diagram shown in Figure 1 illustrates a system which is useful in a number of different applications, such as doppler frequency estimation or "zoom" FFT spectral analysis. It also serves to illustrate the processing power of the VSP. This type of high-performance system is implemented very efficiently by the VSP; most of the blocks in the diagram can be implemented using a single instruction.

## **GENERAL FEATURES**

- High-performance 16-bit digital signal processor

- Architecture optimized for DSP operations

- High-level Vector-oriented instructions

- Block floating-point arithmetic for FFT

## PERFORMANCE BENCHMARKS

| Function                                      | time (µsec) |

|-----------------------------------------------|-------------|

| 1024-point block-floating complex FFT         | , ,         |

| —Single VSP                                   | 3300        |

| —Two parallel VSPs                            |             |

| —Four parallel VSPs                           | 1200        |

| 1024-point integer complex FFT                | 2600        |

| 128-point block-floating complex FFT          | 237         |

| 16 x 16 FCT                                   | 1100        |

| 8 x 8-point 2-D complex FFT                   | 164         |

| 64 x 64-point 2-D block-floating complex FFT  | 18000       |

| 128-point x 128-point complex vector multiply |             |

| 128-point magnitude-square/accumulate         |             |

| 128-point complex modulation or demodulation  |             |

| 4 x 4 matrix multiplication                   |             |

|                                               |             |

## WHY THE VSP IS UNIQUE

The VSP achieves its high performance through a number of unique architectural features. Firstly, the VSP uses a "high-level", vector-oriented instruction set; for instance, "FFT" is a single instruction within the VSP. These types of instructions can greatly simplify the amount of programming effort required to implement signal processing algorithms. Secondly, the VSP provides a block floating-point arithmetic capability which will help retain the original dynamic range of an input signal when performing FFT operations. This typically provides dynamic-range performance significantly greater than that of 16-bit fixed-point integer machines. Finally, the nature of its architecture and instruction set allows additional VSPs to be paralleled on the same bus to increase the signal processing throughput well beyond that of a single VSP.

- Concurrent I/O and arithmetic processing

- Easily paralleled for greater throughput

- Fabricated in two micron DLM CMOS

- <300mW power dissipation

- Powerful hardware and software development tools

FIGURE 1. BLOCK DIAGRAM OF GENERAL COMPLEX DEMODULATION PROCESS IMPLEMENTED EFFICIENTLY BY THE VSP.

## INTRODUCTION

While the signal processing performance of the VSP is quite high, the concept of its operation is straightforward. Data typically is loaded to the VSP as a vector of up to 128 complex samples, operated on by one or more of the VSP's 15 arithmetic instructions, and stored back to external memory. Operating on vectors in external and/or internal RAM, the VSP instruction repertoire includes FFT, vector addition/multiplication, complex conjugate, magnitude square, and modulate/demodulate. These algorithm-level instructions result in compact and highly efficient programs. Block floating-point arithmetic for the FFT gives the VSP superior performance on large transforms as compared to ordinary 16-bit fixed-point processors.

Zoran's focus on providing a complete system solution is reflected in the available hardware and software development tools. A number of software tools are available, including a software simulator and assembler. The VSP Simulator software provides an environment for exploring and learning the capabilities of the VSP, and for testing the functional aspects of an application by generating, processing, and plotting test signal results. Plug-in boards and debugger software work with both the simulator and assembler to allow programs written for the VSP to be run in real-time.

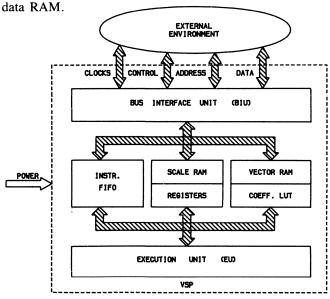

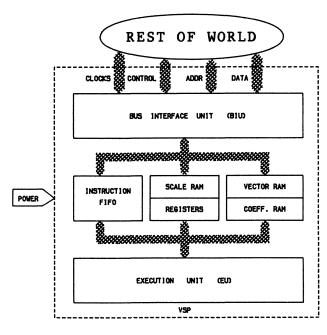

## ARCHITECTURAL FEATURES

The VSP architecture contains three primary functional units as shown in Figure 2: the bus-interface unit (BIU), execution unit (EU), and memory and registers. The BIU handles all communication between the VSP internal resources and the external environment. The EU handles all arithmetic processing. The memory and registers are shared between the BIU and EU, and contain the instruction FIFO, operating registers, and

FIGURE 2. VSP FUNCTIONAL ARCHITECTURE.

## **Bus-Interface Unit:**

- DMA (block transfer) capability

- Separate 64K-word data and program address spaces

- Bidirectional 16-bit address, data, and control buses

## **Execution Unit:**

- Architecture optimized for general vector and FFT butterfly operations

- Internal 17-bit arithmetic precision

- $17 \times 17 = 17$ -bit multiplier

- Two adder/subtractors

- Two 25-bit accumulators

## Memory and Registers:

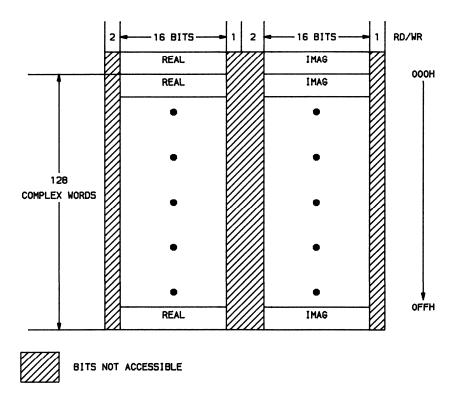

- Internal 128 × 38-bit complex-word RAM

- Four-instruction internal FIFO

- Internal sin/cos look-up table supports up to 1024-point FFT

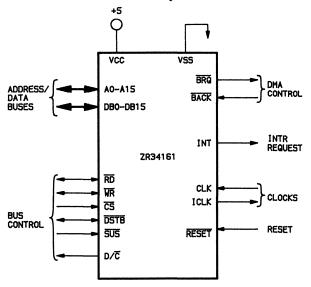

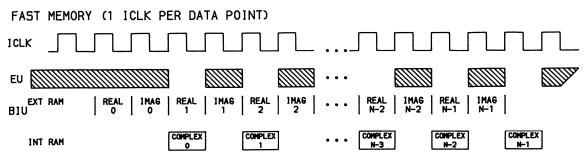

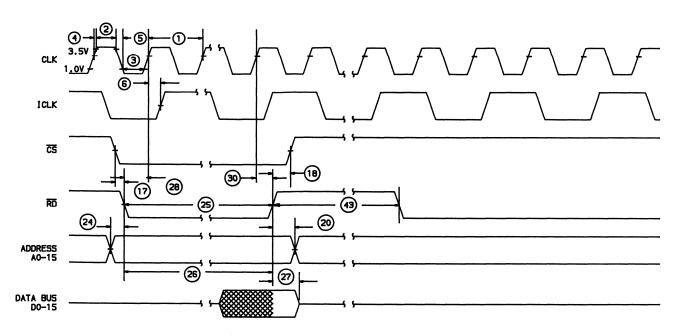

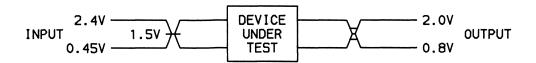

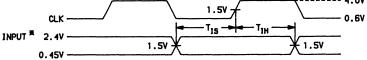

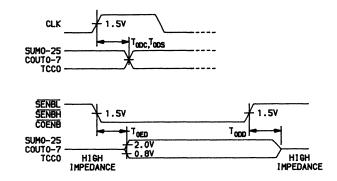

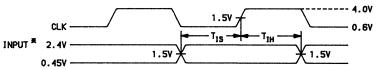

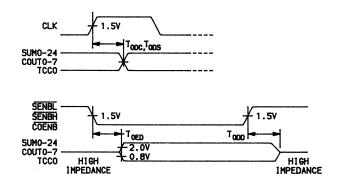

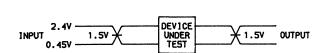

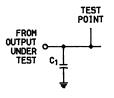

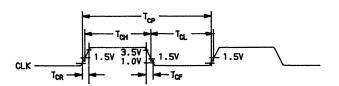

**Bus-Interface Unit:** The VSP is a two-cycle processor, using a maximum 20MHz input clock (CLK). The CLK signal is internally divided by two to create a 10MHz clock which is provided on an output pin (ICLK) and also clocks all internal activity.

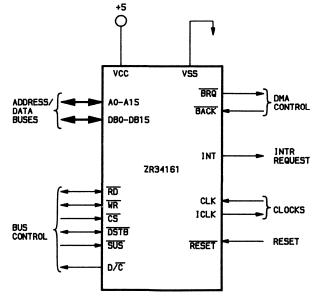

The BIU has a familiar microprocessor-style interface as seen in the logical pinout of Figure 3. It is designed to interface easily to a wide variety of potential host microprocessors and controllers. All instructions to be executed and data to be processed by the VSP first pass through the BIU into the appropriate memory or register location.

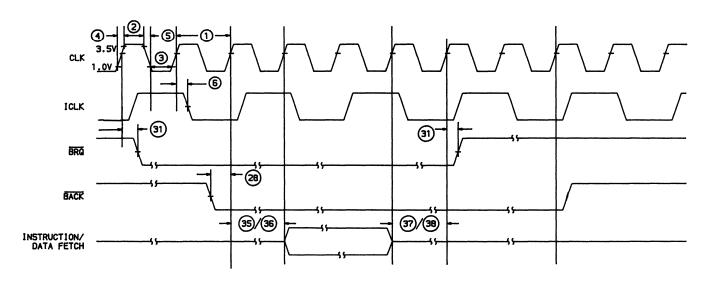

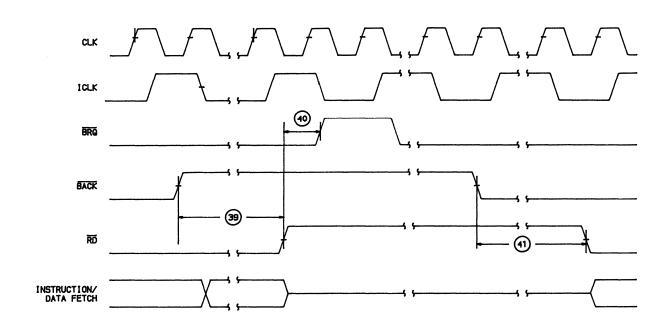

The normal mode of program execution is for the VSP to be given control of the bus, at which time it will fetch its own instructions and data. It requests the bus by asserting the  $\overline{BRQ}$  (bus request) pin, and takes control only after receiving an active  $\overline{BACK}$  (bus acknowledge) signal in response. Once granted control of the bus, the VSP uses its DMA capability to read/write

FIGURE 3. VSP LOGICAL PINOUT.

blocks of external memory. Use of the  $D/\overline{C}$  (Data/Code) pin allows the VSP to access separate 64K word memory spaces: one for data, the other for instructions. When fetching instructions, the  $D/\overline{C}$  pin is LOW; when fetching data,  $D/\overline{C}$  is HIGH.

Three control signals ( $\overline{RD}$ ,  $\overline{WR}$ , and  $\overline{DSTB}$ ) are bidirectional in nature, as controlled by the state of the  $\overline{CS}$  pin. As outputs, the VSP uses these signals for controlling external memory when fetching instructions and data. As inputs, they allow a host processor to access the internal memory and memory-mapped registers of the VSP. To address its internal memory, the host uses the  $\overline{CS}$  (chip select) pin to establish the address pins as inputs.

The INT (interrupt) output pin from the VSP provides an indication to the host processor that one or more of the five internal interrupt bits has been set. The host should read the VSP status register to interpret the source of the interrupt, which in turn clears the INT pin.

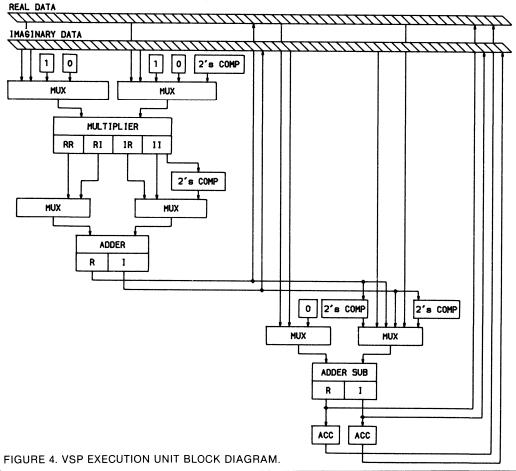

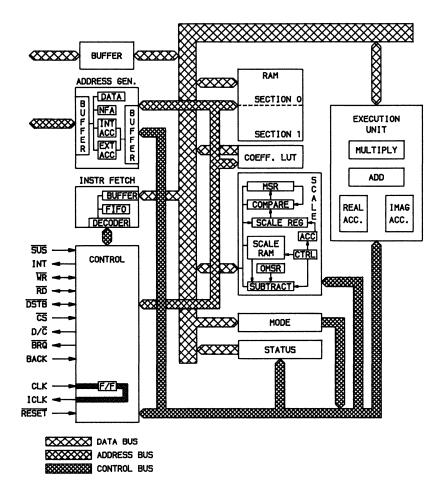

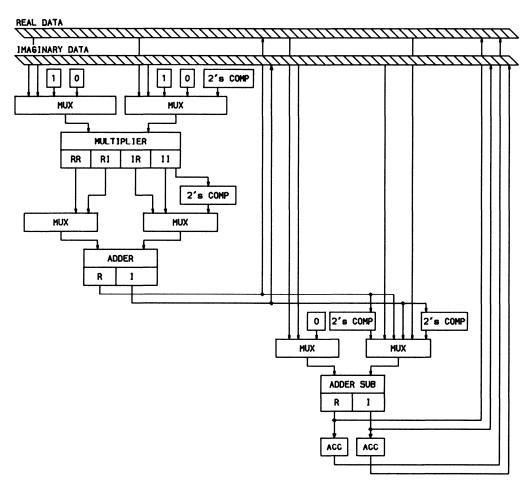

Execution Unit: The execution unit (EU), shown in Figure 4, contains the hardware multiplier, adders, and accumulators for performance of all arithmetic operations. In particular, the EU is organized for efficient vector and FFT-butterfly computations. This is illustrated by the VSP processing rate of 2.5 million FFT-butterfly operations per second. For the FFT, MODLT, and DEMO instructions (Figure 5) the required sine/cosine values

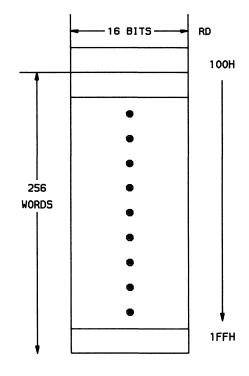

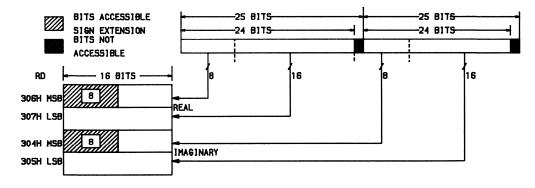

are obtained from the internal look-up table (LUT). The LUT contains 256 17-bit values corresponding to the first quarter cycle of a cosine wave. Together with appropriate logic, this LUT provides all complex weighting factors required for FFTs of up to 1024 points in length.

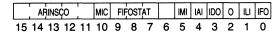

Memory and Registers: The VSP contains a single 16-bit mode register which programs its operating characteristics. The mode register bits are programmed to provide options such as: selecting the speed of external memory, the number of RAM sections in internal memory, and individual enabling of the VSP interrupt bits.

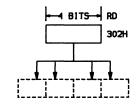

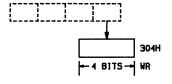

Internal VSP RAM is structured as 128 38-bit complex words, and optionally as two separate sections of 64 complex-words each. Each complex word consists of 19-bit real and imaginary halves. Many of the VSP's instructions affect not only the full complex word, but also the real or imaginary halves separately. Data values are transferred between the VSP and external RAM as 16-bit quantities, but internally the VSP maintains 17 bits of precision (the remaining 2 out of the 19 bits are used for block floating-point arithmetic).

When the internal RAM is logically divided into two 64 complex-word sections, the activities of the BIU and the EU may be overlapped. Specifically, while the EU is performing arithmetic operations on the data in one RAM section, the BIU can transfer data between external RAM and the internal RAM

section not being used by the EU. This overlapping technique provides increased throughput, particularly when slow external memory is being used. (External memory can have an access time that requires one or two ICLKs for data transfer, as programmed in the mode register.)

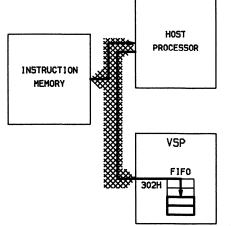

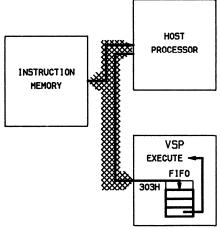

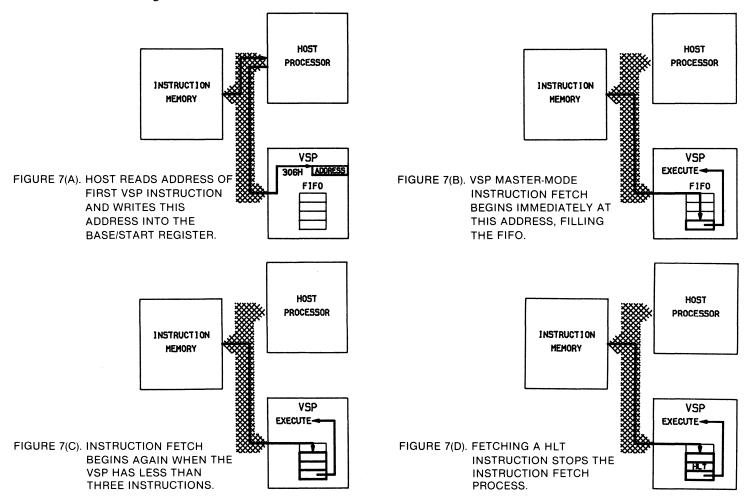

The VSP executes instructions out of its instruction FIFO, in which up to four instructions may be buffered. The FIFO can be automatically replenished by the BIU fetching its own instructions, or can be controlled entirely by the host.

## INSTRUCTION SET SUMMARY

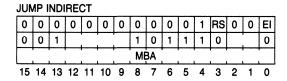

The 23 instructions of the VSP are listed in Figure 5. They are shown grouped into their four logical categories. By selecting values for the parameters associated with these instructions, it is possible to achieve a wide variety of results. For example, when loading a block of data, the parameters associated with the LD instruction allow demultiplexing of multichannel data, storage into the real or imaginary column of the VSP RAM, interpolation of zero values, and bit-reversal reordering for subsequent FFT processing. Similar flexibility is associated with the ST and STB instructions. The STI instruction writes the contents of the VSP's internal registers, including the two accumulators, to external memory. Of the eleven instructions that only operate on internal RAM contents, three—FFT, DEMO, and MODLT—also use the internal LUT. Two special instructions provide support for the vector scaling operations

LD Load LDSM Load Scale/Mode Registers DATA ST Store **MOVEMENT** STB Store Backwards STI Store Information Registers ABS Absolute Value ACCI Accumulate Imaginary ACCR — Accumulate Real CMCN — Complex Conjugate CMLT — Cross Multiply/Accumulate **INTERNAL RAM** DEMO -Demodulate **OPERATIONS FFT** Fast Fourier Transform MGSQ -Magnitude Square/Accumulate MODLT-Modulate SCL Scale SCLT Scale Literal ADDC — Vector Add Complex EXTERNAL/ ADDR — Vector Add Real Vector Multiply Complex/ INTERNAL RAM MLTC — **OPERATIONS** Accumulate MLTR — Vector Multiply Real/Accumulate HLT Halt CONTROL **JMPI** Jump Indirect NOP No Operation FIGURE 5. VSP INSTRUCTION SET.

used in performing large FFTs in block floating-point arithmetic. The four vector add/multiply instructions that use both internal and external memory do not affect external memory contents; only the store instructions do that. The instructions in the control category affect program flow; the NOP and HLT functions are obvious, and the JMPI instruction provides a program looping capability.

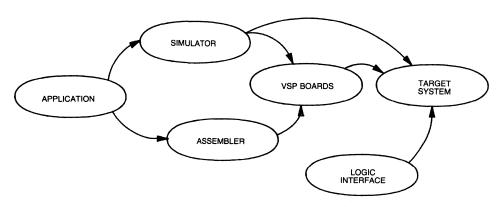

## **DEVELOPMENT SUPPORT TOOLS**

Program development for the VSP is supported through a variety of software and hardware tools. The VSP simulator (VSPS) software is a comprehensive tool for assessing the performance of an entire signal processing system, including the relationship between the VSP and the external environment. The VSPS contains facilities for generating test signal data, executing VSP instructions through a tutorial process, and outputting tabular or graphical data. All internal RAM and register contents may be monitored during VSP program execution, and clock cycles counted for timing purposes. The VSPS is menu-driven, with a command mode for expert use. VSP code can be combined (intermixed) with C or FORTRAN code that simulates external system operations, and linked to the VSPS for subsequent execution. The evaluation board for the IBM PC/AT can be used as an accelerator for the VSPS or in a stand-alone fashion supported by an assembler, debugger, and utility software. A development board, also for the PC/AT, has hardware breakpoint control and I/O buffers to allow real-time debugging of VSP-based system operation.

## SYSTEM INTEGRATION

The VSP is designed as a "loosely-coupled" peripheral processor under the control of either a host microprocessor or simple state machine controller. "Loosely-coupled" means that the host can direct the VSP to perform signal processing functions without tight control over VSP activity. For instance, a host will usually provide a starting address to the VSP which points to the beginning of a signal processing algorithm in external memory. The VSP will fetch its own instructions and data for executing the algorithm and inform the host when it has completed the task.

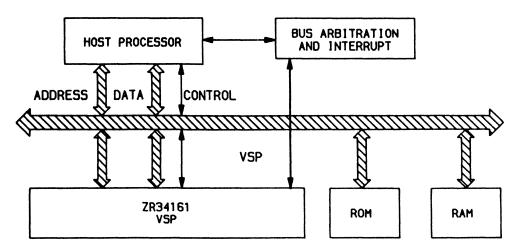

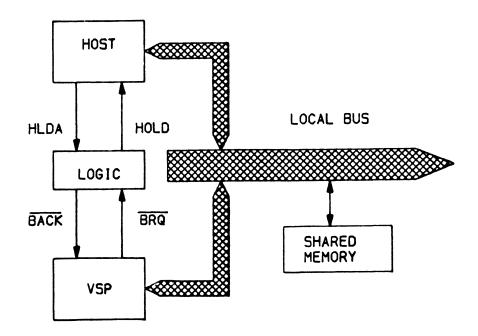

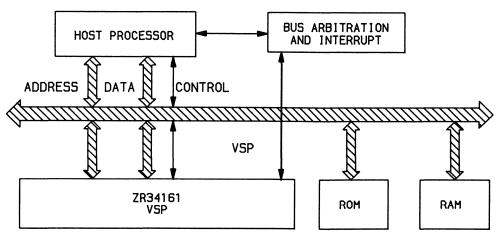

Integration of the VSP into a system requires a minimum of communication between the system host and the VSP. Figure 6 shows how the VSP fits into a bus-oriented system, with the host controlling VSP access to the bus by means of the BRQ and BACK pins. When the host requires the VSP to execute a program, the starting address of the program can be written to the VSP, which then begins fetching instructions and associated data from system RAM and ROM as appropriate. All VSP access to the bus is thereafter managed by the bus arbitration mechanism. VSP programs terminate with a HLT instruction, and the host can be notified of this condition through the INT pin. In this mode of operation, the VSP is a peripheral processor which can perform significantly long computational tasks without close supervision by the host.

## MULTIPLE-VSP APPLICATIONS

The unique nature of the VSP architecture and instruction set support applications which require signal processing performance beyond that which can be achieved with a single VSP. For instance, using two VSPs operating in parallel on a single bus, a 1024-point complex block floating-point FFT can be computed in 1900  $\mu$ sec. Four VSPs can compute the same operation in 1200  $\mu$ sec.

Because each VSP instruction operates on vectors, or arrays of data, the execution-time of each instruction may be relatively long. For instance, it takes the VSP 1850 clocks to execute a 128-point FFT from a single instruction. Because this operation occurs entirely within the VSP, the data bus is free for additional VSPs (or other peripherals) to use.

The hardware architecture to implement this type of system is very similar to the interface shown in Figure 6. However, the single VSP in the figure would be replaced by multiple VSPs. The bus arbiter would then be responsible for arbiting the bus between all of the VSPs connected in the system.

## PROGRAMMING THE VSP

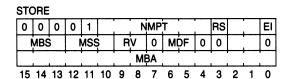

The flexibility of VSP instructions can be illustrated by discussing the use of the LD, ST, FFT and MGSQ instructions to build a simple program for generating a magnitude-squared spectrum. The instruction parameters are listed in Figure 7, and a simplified listing of the program is in Figure 8(a). Each of these instructions can process a vector of up to 128 complex values. Before discussing the use of these instructions, note that the EI parameter is common to all of them. Setting the EI parameter will allow an interrupt signal to be generated when the instruction has finished execution.

For the LD instruction, the NMPT parameter sets the vector size, and the RS parameter selects internal RAM section 0 or 1 if the RAM is logically partitioned into two sections (done by setting a bit in the mode register). The vector is always loaded

into the lowest NMPT locations of the selected internal RAM section. Individual locations of the internal RAM are not addressable using the VSP instructions; they are, however, accessible by the host.

The data is located in external RAM starting at physical word address MBA. The number of words read from external RAM is conditioned by the parameter MDF which specifies whether only the real, imaginary, or full complex word of the internal RAM is to be affected. If only the real or imaginary part of the RAM receives data, then NMPT words are read from external RAM. For a complex-valued vector, 2\*NMPT words will be read, where the VSP assumes the order in external RAM is real-imaginary.

The parameters MBS and MSS allow demultiplexing of multichannel data by selecting blocks of MBS data values spaced MSS values apart. INTRP allows up to three zero-valued elements to be inserted between each sample; ZR can put zeros in either the real or imaginary part of the internal RAM; and ZP can make the last half of the length-NMPT vector zero-valued. The ST instruction has similar features, as indicated by the common parameters in Figure 7.

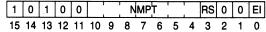

For use with the FFT instruction, both LD and ST have the RV parameter which allows bit-reversal reordering of data values. In combination with the MBS and MSS parameters, this also allows bit-reversal reordering of blocks, or data within blocks—features that are required for performing large or multidimensional FFTs. For the FFT instruction, NMBT is the total number of data values to be processed. If FSIZ, the size of the FFT, is smaller than NMBT, then multiple small FFTs can be performed in a single instruction. With NMBT limited to 128, it is possible to do two 64-point, four 32-point, etc. transforms at once. Parameter I selects forward or inverse transform, R indicates if the input data is bit-reversed in order, and AS specifies fixed-point or block floating-point arithmetic.

FIGURE 6. VSP SYSTEM INTERFACE.

The FFT instruction also has three parameters which play a role in performing large FFTs: the FPS and LPS parameters define the separation between the two data points which are combined in a butterfly operation at the first and last passes through the data, respectively; and RBA selects the starting location in the sine/cosine LUT for obtaining complex weights. Proper use of these parameters does require analysis of the FFT algorithm; however, Zoran supplies a software library for transforms up to length 16384.

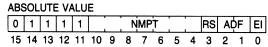

By comparison with the LD, ST, and FFT instructions, the MGSQ instruction has few parameters, and only one is different from those discussed already. Normally the squares of the real and imaginary parts are added and stored in the real part, scaled down by 1/2 to avoid overflow, with the total accumulated in the real accumulator. If ADF is zero then only the accumulator is affected—the values in the internal RAM are unchanged.

| LD<br>(LOAD) | ST<br>(STORE) | FFT<br>(FAST FOURIER<br>TRANSFORM) | MGSQ<br>(MAGNITUDE<br>SQUARE/<br>ACCUMLUATE) |

|--------------|---------------|------------------------------------|----------------------------------------------|

| NMPT         | NMPT          | NMBT                               | NMPT                                         |

| RS           | RS            | RS                                 | RS                                           |

| INTRP        |               | El                                 | ADF                                          |

| El           | El            | FPS                                | El                                           |

| MBS          | MBS           | LPS                                |                                              |

| MSS          | MSS           | RBA                                |                                              |

| RV           | RV            | FSIZ                               |                                              |

| MDF          | MDF           | AS                                 |                                              |

| ZR           |               | !                                  |                                              |

| ZP           |               | R                                  |                                              |

| MBA          | MBA           |                                    |                                              |

FIGURE 7. EXAMPLE OF VSP INSTRUCTION PARAMETERS.

| LD   | NMPT:128 | RS:0 | MDF:2  | ZR:1   | MBA:0;  |

|------|----------|------|--------|--------|---------|

| FFT  | NMBT:128 | RS:0 | FPS:64 | LPS:1; |         |

| MGSQ | NMPT:128 | RS:0 | ADF:2; |        |         |

| ST   | NMPT·128 | BS:0 | RV·1   | MDF·2  | MRA-256 |

(A) MAGNITUDE-SQUARE SPECTRUM.

DEFAULT NMPT:128 RS:0 INTRP:0 EI:0 MDF:3 ZR:0 ZP:0;

|                            | DEFAULT NMBT:128 FSIZ:128 AS:1 I:0 R:0; |          |         |         |         |               |  |  |

|----------------------------|-----------------------------------------|----------|---------|---------|---------|---------------|--|--|

| (0)                        | LDSM                                    | NMPT:1   | UP:1    | MD:1    |         | MBA:16383;    |  |  |

| (1)                        | LD                                      | NMPT:128 | MBS:1   | MSS:2   | RV:0    | MBA:IN;       |  |  |

| (2)                        | FFT                                     | NMBT:128 | FPS:64  | LPS:1   | RBA:0;  |               |  |  |

| (3)                        | ST                                      | NMPT:128 | MBS:1   | MSS:2   | RV:0    | MBA:IN;       |  |  |

| (4)                        | LD                                      | NMPT:128 | MBS:1   | MSS:2   | RV:0    | MBA:IN + 2;   |  |  |

| (5)                        | FFT                                     | NMBT:128 | FPS:64  | LPS:1   | RBA:0;  |               |  |  |

| (6)                        | ST                                      | NMPT:128 | MBS:1   | MSS:2   | RV:0    | MBA:IN + 2;   |  |  |

| (7)                        | LD                                      | NMPT:128 | MBS:128 | MSS:128 | RV:0    | MBA:IN;       |  |  |

| (8)                        | FFT                                     | NMBT:128 | FPS:1   | LPS:1   | RBA:0;  |               |  |  |

| (9)                        | ST                                      | NMPT:128 | MBS:1   | MSS:2   | RV:1    | MBA:OUT;      |  |  |

| (10)                       | LD                                      | NMPT:128 | MBS:128 | MSS:128 | RV:0    | MBA:IN + 256; |  |  |

| (11)                       | FFT                                     | NMBT:128 | FPS:1   | LPS:1   | RBA:14; |               |  |  |

| (12)                       | ST                                      | NMPT:128 | MBS:1   | MSS:2   | RV:1    | MBA:OUT + 2;  |  |  |

| (B) 256-POINT COMPLEX FFT. |                                         |          |         |         |         |               |  |  |

FIGURE 8. VSP PROGRAMS FOR FFT.

## PROGRAM EXAMPLES

Figure 8 lists two programs—one simple, the other more involved—both concerned with using the instructions discussed above. The instruction format includes only those parameter values essential to reading the listing, and also those parameters which change value in succeeding instructions. The remaining parameters are set with the "DEFAULT" directive.

In Figure 8(a) the magnitude-squared spectrum for 128 real-valued time samples is computed. That the input samples are real is indicated by MDF:2 in the LD instruction. The 128 real samples are located in external memory starting at physical address zero, and are loaded in normal order (RV:0). A full 128-point FFT is performed, as indicated by the FPS value of 64 and the LPS value of 1. In the FFT instruction, AS:1 selects fixed-point arithmetic with a scaling by 0.5 (right-shift by one bit) at each stage. The magnitude-squared values are stored in the real part of the internal RAM (ADF:2) by the MSGQ instruction. The ST instruction puts the spectral values into external RAM starting at address 256, and does a bit-reversal reordering in the process (RV=1).

To facilitate discussion of the program example in Figure 8(b), the key instructions have been numbered; this numbering is not used for actual VSP programs. The program for the 256 complex-point FFT performs two separate 128-point FFTs and then combines the results to obtain the spectral values for the full 256-point transform. The procedure is based upon converting an N-point transform into two N/2-point transforms by grouping the input samples into even- and odd-indexed sets—a procedure known as decimation-in-time, or DIT. For simplicity, block floating-point scaling is not performed; instead, a fixed shift by one bit is performed in each pass (AS:1).

Instruction (0) simply programs the VSP mode register to the desired contents. Instruction (1) loads every other sample starting at the beginning of the vector—external memory location IN—to give the even-indexed samples. Instruction (4) loads the odd-indexed samples starting at IN+2 (complex samples occupy two successive memory locations in external RAM). Each 128-point vector is transformed and stored back to external RAM, overwriting the time samples. This process is done with instructions (1) to (6). When the transform values are stored back to external RAM they are not bit-reversed reordered; this allows adjacent elements in each 128-point vector of transform values to be combined using a single butterfly operation.

Instructions (8) and (11) have FPS=LPS:1 to indicate the performance of a single stage of butterflies operating on adjacent samples in the vector—a sample separation of 1. The final 128-point vector requires a different set of complex weights from the previous vector; hence, in instruction (11) an offset into the LUT—RBA:14—is specified in order to get odd powers

of the 256th root of unity. The transform values are stored in bit-reversed order in a 256-sample block starting at address OUT—instructions (9) and (12). Because each 128-point vector is separately reordered, the overall FFT operation is not an in-place procedure. The complete 256-point complex FFT computation requires less than 650 microseconds.

The use of IN and OUT for memory base reference is an assembler feature—the assembled program will have direct memory references. To use the 256-point FFT program to operate on different segments of external memory would require either modification of addresses by the host or duplication of the program code for each segment. The second option is actually very reasonable because of the small size of VSP programs. In a situation where the host maintains double buffers for both input and output, it would only be necessary to have two copies of the program—one for each pairing of an input and output buffer. The first option, host modification of data addresses in VSP programs stored in external memory, is aided by the fact that address references in VSP instructions always occupy the last word of the three-word instruction.

## **PROGRAM SIZE**

Conventional DSP microprocessors have scalar-oriented instruction sets which need loop-control code in order to operate on the blocks of data processed in the majority of DSP algorithms. Because DSP processors are optimized to perform multiply-accumulate operations, the time required for loop-control arithmetic is frequently a very significant percentage of the total execution time. For this reason, time-optimized programs are written as straight-line code. Naturally, this results in programs of considerable size.

Table 1 compares statistics for FFT programs on the VSP and the TMS32020. The first two entries in the table correspond

to the programs just discussed. The advantages of vector-oriented instructions over scalar-oriented instructions with loop control are clearly evident. However, even when straight-line code is employed, the VSP still enjoys a significant speed advantage. Of course, the size of the straight-line coded 256-point FFT on the TMS32020 is orders of magnitude greater than the VSP program size. The next generation scalar-oriented processors may have a factor of two improvement in execution time, but program size will remain substantially the same.

## **BLOCK FLOATING-POINT**

The highly repetitive and sequential operations of the FFT algorithm present a well-known source of overflow and roundoff noise accumulation problems. In ordinary fixed-point arithmetic the strategy for countering overflow is a scaling of each sample by 0.5 at each stage. This procedure is not sufficient to guarantee no overflows, and in many cases results in unnecessary loss of accuracy. The VSP allows fixed-point computation with fixed scaling by 0.5 in the FFT, but more importantly the VSP supports block floating-point (BFP) arithmetic for FFT computation. In BFP arithmetic an exponent, or scale factor, is associated with a block or vector of data, rather than with each element as in full floating-point arithmetic.

The worst-case growth in value after a butterfly operation is about 1.5 bits. Both real and imaginary halves of the VSP RAM contain 2 bits to hold this overflow. After the full complex vector has been processed in a stage of the FFT there will be a maximum overflow count for the vector. When the vector is accessed again, either for the next FFT stage or for storage to external RAM, each element of the vector is right-shifted by 0, 1, or 2 bits in accordance with the overflow count. At the conclusion of the FFT the total number of shifts performed is placed in one of the 4-bit nibbles of the scale register, which can be written to external RAM. The maximum expected shift

|                                        | Program Memory Red<br>TMS32020              | quirement (Words)<br>ZR34161 | VSP<br>Advantage | Execution Tin<br>TMS32020 | ne (millisec)<br>ZR34161 | VSP<br>Advantage |

|----------------------------------------|---------------------------------------------|------------------------------|------------------|---------------------------|--------------------------|------------------|

| 128-Point<br>Magnitude Spectrum        | 160 (looped)                                | 12                           | 13x              | 4.375                     | 0.2636                   | 16x              |

| 256-Point FFT                          | 124 (looped)                                | 39                           | 3x               | 8.483                     | 0.6328                   | 13x              |

| 256-Point FFT (straight-line)          | 20,000                                      | 39                           | 513x             | 4.519                     | 0.6328                   | 7x               |

| 1024-Point FFT<br>Fixed-point          | 20,000<br>(uses 256-Point<br>as subroutine) | 300                          | 66x              | 31.82                     | 2.4                      | 13x              |

| 1024-Point FFT<br>Block Floating-Point | _                                           | 600                          | Not Computed     | _                         | 3.3                      | Not Computed     |

TABLE 1. Program Size and Execution Comparison.<sup>1</sup>

<sup>1</sup> PORTIONS OF THE DATA IN THIS TABLE OBTAINED FROM: "IMPLEMENTATION OF FAST FOURIER TRANSFORM ALGORITHS WITH THE TMS32020", DIGITAL SIGNAL PROCESSING APPLICATIONS WITH THE TMS32020 FAMILY.

count for a 128-point FFT is 8, giving an effective 48 dB of "head-room". With 17 bits precision for each VSP RAM word there is a total dynamic range of 150 dB in computing a 128-point FFT.

For FFTs larger than 128 points the VSP contains a scale RAM which can hold 64 scale nibbles—sufficient for processing all longer-length FFTs. When vectors of 128, or fewer, elements are to be combined in the process of computing a large FFT, the scale RAM and the maximum scale register are used by the SCL instruction to shift the elements of the vectors so that a single scale factor, or exponent, applies to the total collection of sample values.

The benefits to be obtained from BFP arithmetic operation are summarized in Table 2. The values are for the signal-to-computational-noise ratio at the output of an FFT of the size indicated. The input signal is assumed to be white noise. The results for BFP arithmetic are based on an expected number of scalings. Because scaling by 0.5 is not required at each stage, the discretionary scaling policy of BFP arithmetic results in the minimum reduction in signal amplitude. As Table 2 illustrates, the expected performance of BFP arithmetic is substantially superior to that of a fixed scaling policy. In many applications the actual signal-to-computational-noise ratio for BFP arithmetic will be significantly better than is indicated by the values in Table 2.

| FFT<br>Size | Output Sigr<br>Block Floating<br>Point | nal/Noise (dB)<br>Scale by 1/2<br>at each Stage |

|-------------|----------------------------------------|-------------------------------------------------|

| 32          | 78                                     | 71                                              |

| 64          | 76                                     | 68                                              |

| 128         | 75                                     | 65                                              |

| 256         | 74                                     | 62                                              |

| 512         | 73                                     | 59                                              |

| 1024        | 72                                     | 56                                              |

| 2048        | 71                                     | 53                                              |

| 4096        | 70                                     | 50                                              |

| 8192        | 69                                     | 47                                              |

| 16384       | 68                                     | 44                                              |

TABLE 2. FFT SNR Performance Comparison.<sup>2</sup>

## **VSP APPLICATION EXAMPLES**

In addition to its powerful FFT instruction, the other vectororiented instructions of the VSP are ideally suited to the naturally occuring operations of most digital signal processing procedures. The two examples presented here are illustrative of the wide applicability of the ZR34161.

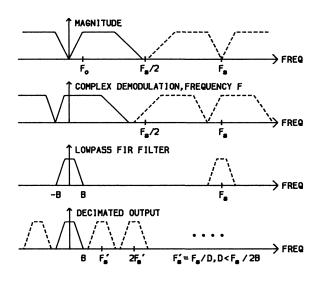

Zoom FFT: "Zoom" FFT is the label used for the process of shifting a signal spectrum down in frequency, lowpass filtering and decimating, and then applying an FFT to view in detail a small region of the original spectrum. This process is described spectrally in Figure 9(a). Although much the same objective could be realized by performing a large FFT and selecting only the spectral components of interest, the zoom FFT approach requires much less data memory and can better isolate low-level spectral lines from the leakage effects of strong spectral peaks. A flow diagram of the signal processing involved is shown in Figure 9(b). The block diagram of Figure 1 shows more descriptively the process taking place in the complex demodulation and the decimation/lowpass filter blocks.

To be specific, consider the requirements and performance of a 10x zoom with a 128-point FFT—equivalent to a 1280-point discrete Fourier transform. The FIR decimating filter is specified as having 60 dB stopband rejection and 0.5 dB peak-to-peak ripple over a two-sided passband that is 90% of the sampling frequency. A single FIR filter would be of length 395; by cascading two FIR filters which respectively decimate by 2 and 5, the desired frequency response can be obtained with FIR filters of lengths 37 and 79. The operating sequence is to frequency shift every 10 input samples, then cycle the decimate-by-2 FIR filter every 2 samples to produce 5 values which are processed by the decimate-by-5 FIR filter which ultimately produce a single sample. This set of computations is done 128 times to produce the input data for the FFT computation.

The complex modulation—frequency shifting—and FIR filtering can be done by the VSP in 10.36 msec assuming that the host does all circular buffer management and address modification for the VSP program. In another 0.237 msec the VSP can compute the FFT and store the complex spectral values in external memory. With the host managing all data buffers and system I/O, the VSP can perform the 10x 128-point zoom FFT at more than a 120 kHz input sample rate. The 128 spectral values are centered about the shift frequency which, using the VSP's DEMO instruction to do the shifting, can be any integer multiple of  $f_{\rm s}/1024$ , where  $f_{\rm s}$  is the sampling frequency.

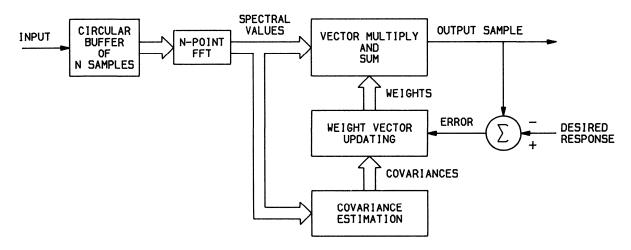

Frequency-domain LMS: Although simple to implement, the ordinary time-domain LMS (least-mean-squared) adaptive filter has unfortunate convergence properties. To speed up convergence, while reducing noise induced by fluctuations of weight values, several modifications to the elementary LMS process have been introduced. The frequency domain procedure—FLMS—improves convergence the most, and has the lowest computational burden of the modified LMS procedures.

<sup>2</sup> PORTIONS OF THE DATA IN THIS TABLE OBTAINED FROM: OPPENHEIM, A., AND SCHAFER, R., DIGITAL SIGNAL PROCESSING.

The computational steps for the FLMS procedure, as outlined in Figure 10, are perfectly matched by the VSP instruction set. In addition to the FFT instruction, the operations of complex conjugation, vector multiplication and addition, and magnitude-squared are key elements in the FLMS adaptive filter algorithm. The key to the improved convergence rate is the updating of the estimated covariance matrix; by assuming this matrix diagonal it is the variances of the spectral components which are estimated at each step. The spectral components influence the updated values of the filter weighting coefficients in inverse proportion to their variance; this effectively whitens the spectral values and forces approximately equal time constants for all filter weighting coefficients.

Assuming that the host manages the sample buffers, the VSP can implement a 32-tap FLMS adaptive filter with 4700 updates/second, and a 64-tap filter with 2500 updates/second. Because the FLMS approach achieves convergence with only one-half to one-third the number of adaptions of the ordinary LMS approach, the FLMS implementation on the VSP indicates a convergence time equivalent to a time-domain LMS filter operating at 14100 updates/second for 32 taps, or 7500 updates/second for 64 taps.

(A) SPECTRAL DESCRIPTION OF THE ZOOM FFT.

(B) SIGNAL PROCESSING BLOCK DIAGRAM.

FIGURE 9. ZOOM FFT APPLICATION.

FIGURE 10. FREQUENCY-DOMAIN LMS ADAPTIVE FILTERING.

## **VSP SIMULATOR**

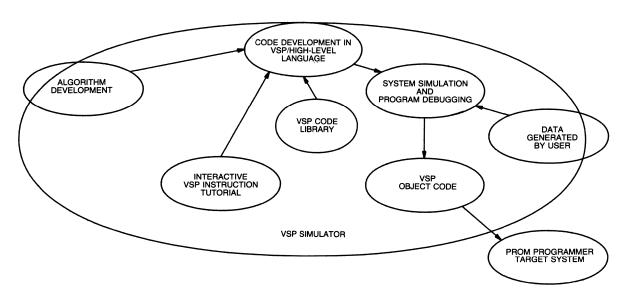

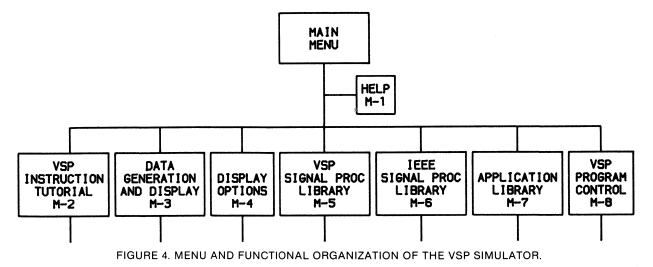

The Vector Signal Processor Simulator (VSPS) software provides a comprehensive set of tools to support the user during all phases of VSP program development and system performance analysis.

## **FEATURES**

- Full simulation of VSP instructions and operation

- Menu-driven, with command mode for expert use

- Generation of test signal samples

- Interactive specification/execution of VSP instructions

- Graphics plotting for time and frequency domain samples

- Simulation of host operations with embedded user program

- Libraries of VSP programs and floating-point routines

- Full display of VSP internal RAM/registers and timing

- Resident on PC/AT under MS-DOS and VAX under ULTRIX and VMS

The VSPS provides an environment that encourages the user to explore system performance characteristics by executing VSP programs on test signals or actual data values. Test signal samples can be generated using a flexible process which automatically maintains normalization of 16-bit values; the samples then can be processed by VSP instructions that are specified and executed interactively. Both the input signal samples and the VSP-processed results can be printed and plotted. Initial use of the VSPS is facilitated by its menu-driven operation. Expert use is supported by a command capability with macro facility. Customization is possible by embedding a user-coded program within a copy of the VSPS, and performing both host and VSP functions with the full support of VSPS tools.

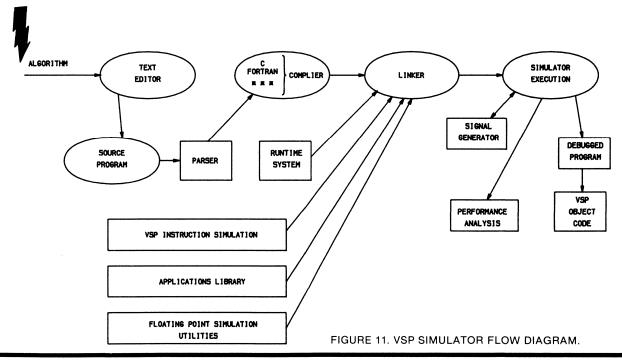

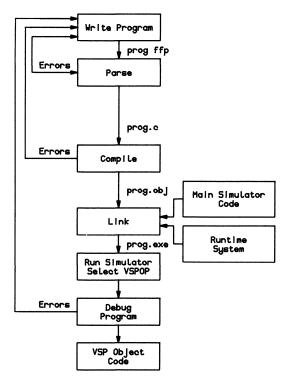

The scope of the VSPS's capabilities can be illustrated by discussing the steps for creating and running a user-coded program as outlined in the flow diagram in Figure 11. The source code can be either FORTRAN or C, and the program can be composed of alternating sections of VSP and non-VSP operations. One possible sequence would be generation of special signal data (or reading of actual data from a disk file), simulation of host operations, execution of a VSP program, simulation of additional host operations, and then display of the results in a user-determined format. The full features of the VSPS, such as signal generation and graphics plotting, are available both before and after running the user program.

In Figure 11, the mixed VSP/host code source program is seen to be processed by a parser which converts the VSP code into calls to the instruction simulation routines. The host code is left unchanged in the high-level language in which it was written. The parsed file is then compiled and linked with the VSPS object modules to create an executable module. The executable module contains the entire VSPS plus the user's program. Upon executing this customized version of the VSPS, the user program can be selected from the main menu. User-programmed input and output will appear on the screen as during any normal FORTRAN or C program execution. VSPS options for selecting the display of internal RAM and registers, and for singlestepping the program execution are still available. When the user's VSP program is running correctly, the code can be converted into one of a number of different output formats for use with a PROM programmer.

In certain applications it is important to measure roundoff effects in fixed-point arithmetic, or even in the block floating-point arithmetic used in FFT calculations. This is facilitated by the inclusion of selected routines in the VSPS from the floating-point IEEE signal-processing library. Thus, for example, power spectrum calculations may be done using both a VSP program and the IEEE program, and the results compared. Comparisons of vectors are supported in the VSPS through a facility to print or plot differences between vectors.

Clock-cycle counts and bus-usage statistics can be provided by the VSPS so that real-time operations and host-VSP interactions can be analyzed. Debugging of a VSP program is aided by a range of display options which allow instructions to be executed in single-step fashion, and which allow viewing of all affected RAM and register locations. Other system features, such as simulation of multiple-VSP configurations and an external memory queue for VSP instructions, are also supported.

## **ASSEMBLER**

The ASM-161 assembler produces an Intel hex format output file which can be loaded into the RAM on the VSPE-161 board or the VSP simulator; a listing file is also provided. Assembler directives support setting the program location counter, as well as allocating memory locations for constants and other data.

The DEFAULT directive is specific to the VSP instruction format in which several parameter values must be specified. Often these parameter values are fixed for much or all of a program. With the DEFAULT directive, parameter values can be set for all instructions which require the parameter, or only for specific instructions. This technique is illustrated in the previous program example in Figure 8(b). Alphanumeric labels for program lines are supported; labeled instruction lines are the target of a JMPI (jump direct) instruction. Labels are also used as symbolic memory location references.

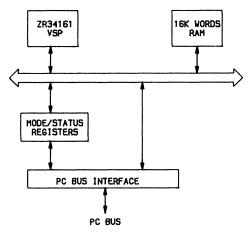

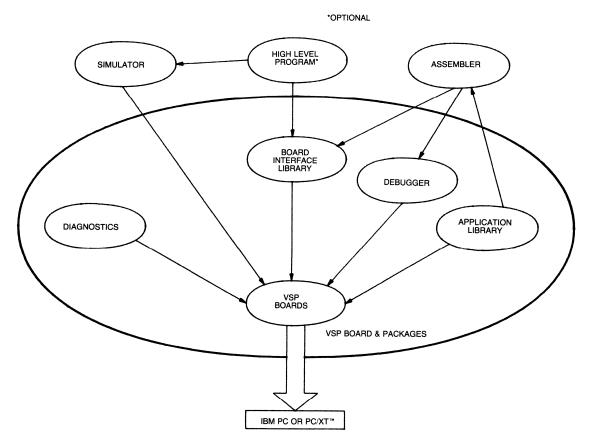

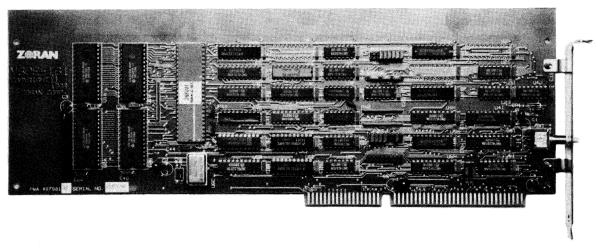

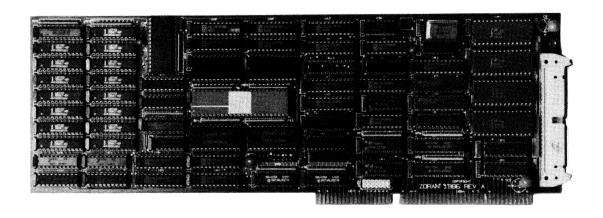

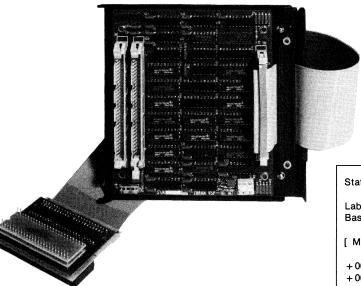

## **VSP EVALUATION PACKAGE**

The Vector Signal Processor Evaluation Package (VSPE-161) consists of a plug-in board and support software compatible with the IBM PC/XT or PC/AT. The board contains a ZR34161 processor, 16K words of 120 nsec static RAM, local bus arbitration logic, and I/O status ports. The software provides a complete development environment consisting of a debugger, utilities for controlling board functions, and a library of example VSP programs. The VSPE-161 board can also function as a hardware accelerator for the VSP Simulator software.

**Debugger:** Testing of programs on the VSPE-161 board is greatly facilitated by the Debugger software. The Debugger provides a command-driven environment for:

- loading and saving program and data files

- creating test signal samples in the board's RAM

- displaying, modifying, and moving memory contents

- controlling the execution of a VSP program through singlestep and breakpoint-setting features

- plotting of real/complex data in the board's RAM

- composing macros of Debugger commands and other macros.

A typical sequence of operations with the Debugger would begin with the loading of a hex file produced by the Assembler. Data samples to be processed by the VSP program can be loaded from a file, typed in from the keyboard, or produced with the signal-generation command. Any segment of the board's memory can be plotted on the screen as real or complex data. Program execution is controlled either with the 'RUN' command and breakpoint settings, or with the single-step command. Program performance can be monitored by displaying the contents of board memory, VSP memory, or VSP registers. Minor program editing can be done using the disassemble command to view instructions, and the interactive-fill command to type in replacement hex programs.

Utilities: A library of utility procedures is provided for controlling and communicating with the board from a user program running under PC-DOS. The utility routines are written in C, and can be invoked from a source program coded in Microsoft C or FORTRAN. There are eleven routines for file reading and writing. An example application is included with the utilities to illustrate their use. The user program can simulate the host operations in a VSP-based system, and have all VSP code executed by the VSPE-161 board.

**Example VSP Programs:** The source code for several VSP programs is included in the VSPE-161 package. The detailed comments which annotate the listings provide full details on the background of the algorithm, and on the procedures for adapting the programs to the user's needs. These programs serve as examples of assembler format and VSP programming style. They also provide immediately available programs for use with the assembler and debugger in learning the application of the VSPE-161 package. Included in the library are complete programs for the FFT of 128, 256, and 1024 complex points.

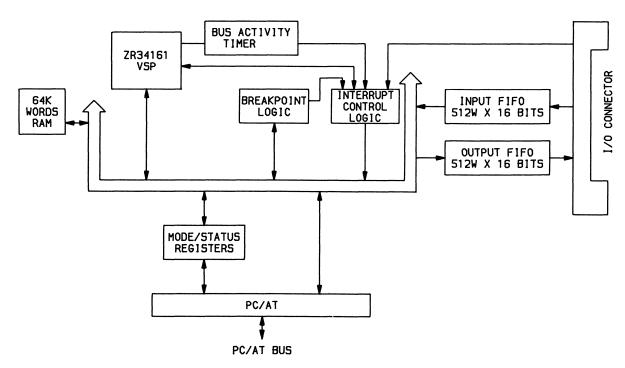

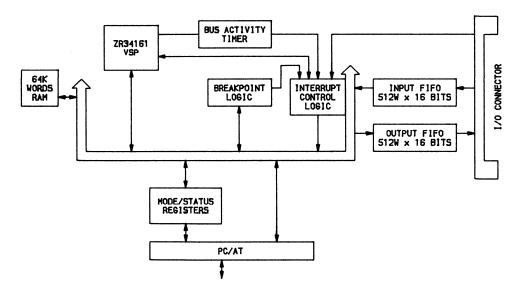

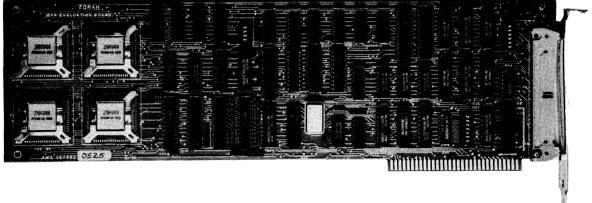

## VSP DEVELOPMENT PACKAGE

The Vector Signal Processor Development Package (VSPD-161) consists of a plug-in board and support software compatible with the IBM PC/AT. The board contains a ZR34161 Vector Signal Processor running at 20MHz, 64K words of 45 nsec static RAM, local bus arbitration logic, hardware breakpoint logic, two 512 word by 16-bit parallel I/O FIFO buffers, and I/O status ports. A 50-pin connector provides data I/O and control lines to the external system. The software provides a complete

**ZORAN**

development environment consisting of a debugger, utilities for controlling board functions, and a library of example VSP programs. The VSPD-161 board can function as an element of an external real-time system, thus providing the capability for system-level program development and debugging.

FIFO Usage: Real-time I/O is accomplished with the dual 512-word FIFOs. These FIFOs are mapped into the data RAM address space of the VSP so that vector transfers may be made directly to and from the external system. The FIFOs are also mapped to the PC/AT address space so that their contents may be set and read during program debugging, for example.

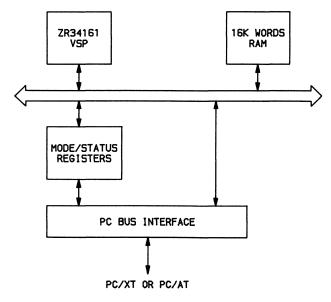

FIGURE 12. VSPE BOARD DIAGRAM.

PC/AT Interface: Full access to board functions and memory is available through the PC/AT bus. Four I/O ports are used for board configuration and operation control. Setting bits in the configuration port allows internal VSP RAM/registers and onboard RAM to be addressed in a single 64K byte segment of the PC/AT address space. The operation control port can specify breakpoint action on VSP address generation—as specified by the value in the breakpoint register—or on an external event such as reading a tagged word in the input FIFO. Strobe and board status registers control and monitor the FIFOs and bus on the VSPD-161 board.

Breakpoint Operation: The on-board breakpoint register is set from the PC/AT. When the VSP reads or writes to the specified address, the VSP is stopped by denying it access to the bus, and interrupt signals go to the PC/AT and the external connector. VSP activity is resumed after a PC/AT write to the strobe register port. Externally-initiated breakpoints come from tagged data in the input FIFO, or from the IRQBRK pin on the external connector.

Support Software: Support software consists of VSPD-specific utilities such as a debugger, board control and communication drivers, and a VSP program library. The function of this software is very similar in nature to the software described in detail in the VSPE section. Programs assembled using the VSP assembler may be loaded onto the VSPD board and executed using the debugger software. Alternatively, high-level language programs maybe written (in C or Fortran for instance) which call the VSPD board and control its operation.

FIGURE 13. VSPD-161-BLOCK DIAGRAM.

## UPDATES FROM 30 JULY 1986 ENGINEERING DATA

This section highlights changes or updates to ZR34161 Engineering Data relative to the previous (30 July 1986) publication. It is provided to allow engineers to scan these updates without reading the document in fine detail. Minor updates incorporated simply for clarity purposes are not highlighted.

#### **CHAPTER 3:**

- Add initial condition to Table 2 (Section 3.1).

- Modify CLK description (Section 3.2).

- Add "status bits notes" section at end of Section 3.3.1.

#### **CHAPTER 4:**

- Add to description of RS parameter (Section 4.2).

- Add NOTE to LDSM instruction description (section 4.3).

- Add NOTE to ADDR, MLTC, and MLTR instruction description (Section 4.4).

- Modify CMCN instruction description (Section 4.5).

- Modify bit in DEMO instruction field (Section 4.5).

- Modify bit in MODLT instruction field (Section 4.5).

- Add footnotes to Table 6 (Section 4.7).

#### **CHAPTER 5:**

- Modify host-access recovery-time specification (Section 5.1).

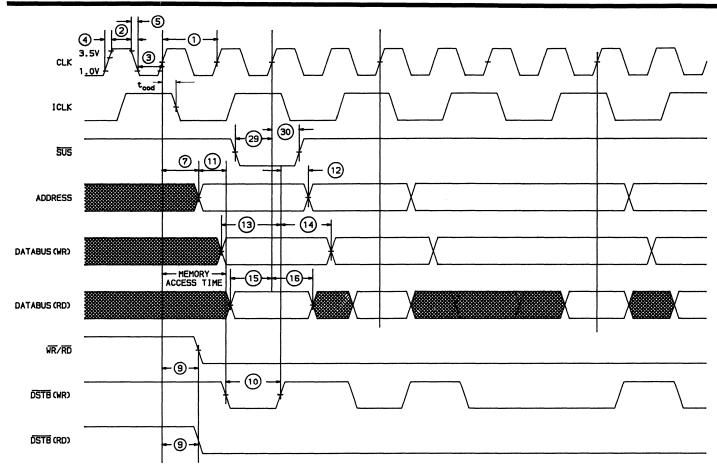

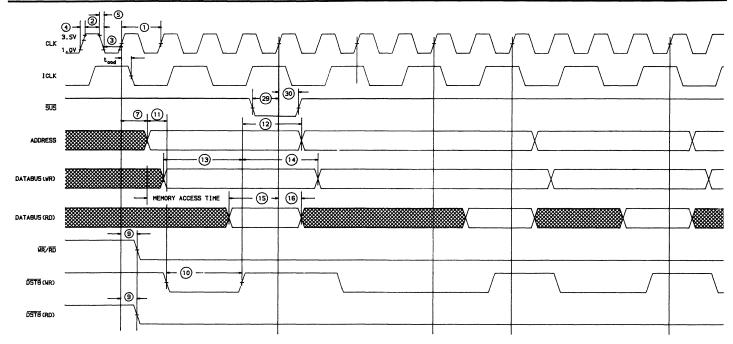

- Modify specifications for timing signal numbers 13, 25, 26, 39

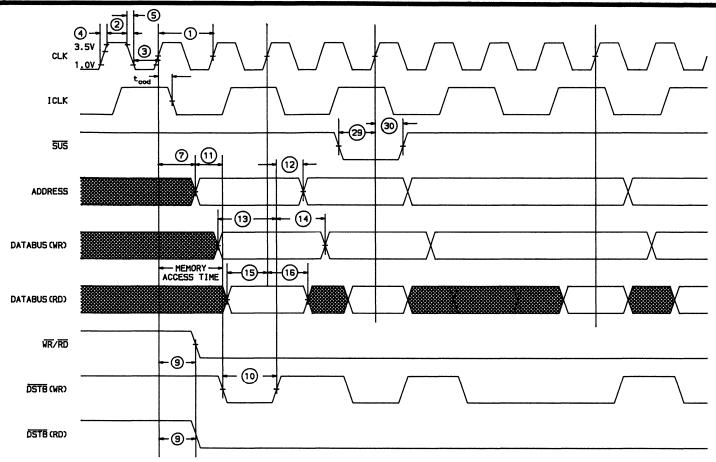

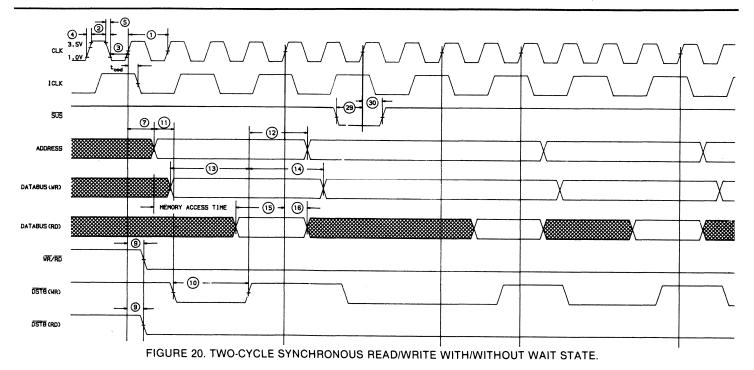

- Redraw (for clarity) VSP master-mode read/write timing diagrams (Figures 17-20) (Section 5.2).

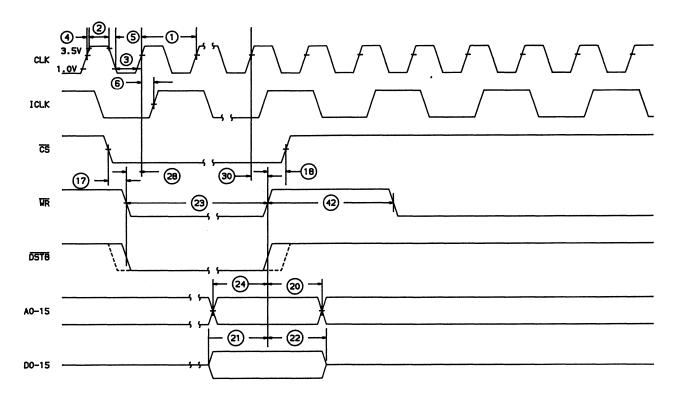

- Redraw (for clarity) host read/write access of VSP resources timing diagrams (Figures 21-22) (Section 5.2).

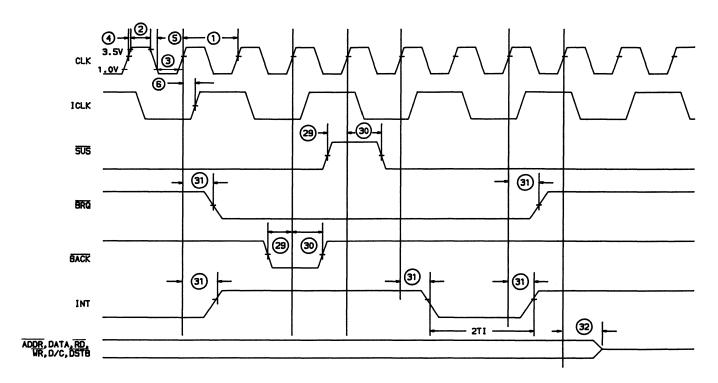

- Redraw (for clarity) preemptive bus arbitration timing diagram (Figure 25) (Section 5.2).

## TABLE OF CONTENTS

| CHAPTER 1 | Processor Overview                                               | 3.1       | VSP Initial Conditions                  |

|-----------|------------------------------------------------------------------|-----------|-----------------------------------------|

| 1.1       | Functional                                                       | 3.2       | Interface Signals                       |

| 1.2       | Architecture                                                     | 3.3       | Internal Memory and Registers35         |

|           | 1.2.1 Bus-Interface Unit23                                       |           | 3.3.1 Status Register                   |

|           | 1.2.2 Execution Unit                                             |           | 3.3.2 Mode Register                     |

|           | 1.2.3 Memory and Registers25                                     |           | 3.3.3 Data RAM38                        |

| 1.3       | Instruction Set                                                  |           | 3.3.4 Instruction FIFO39                |

| CHADTED 1 | Eurotional Operation and Operating                               |           | 3.3.5 Next Fetch Address Register39     |

| CHAPTER 2 | Functional Operation and Operating                               | •         | 3.3.6 Instruction Base/Start Register39 |

| 2.1       | Modes         27           Modes of Instruction Fetch         27 |           | 3.3.7 Scale RAM40                       |

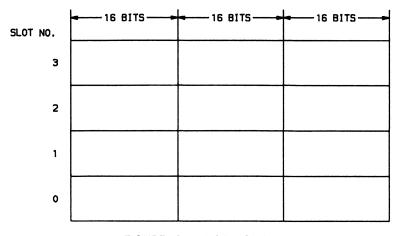

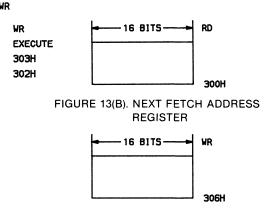

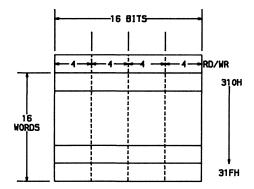

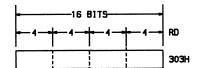

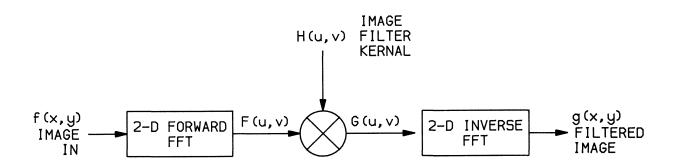

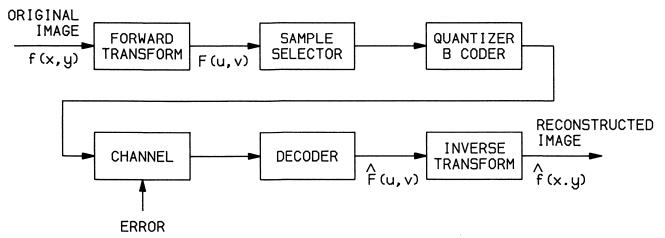

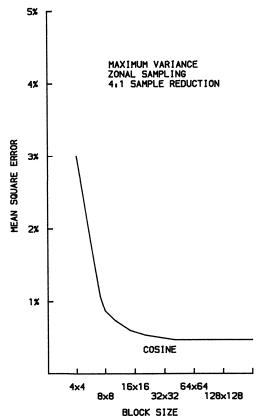

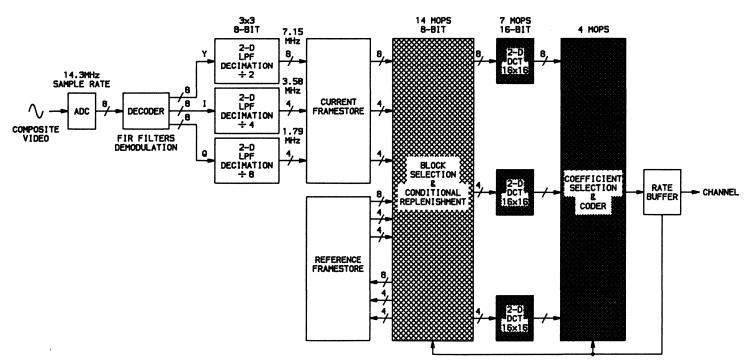

| 2.1       | 2.1.1 Slave Mode                                                 |           | 3.3.8 Scale Register                    |